关于Vivado的综合设置使用总结

judy 在 周四, 11/25/2021 - 09:14 提交

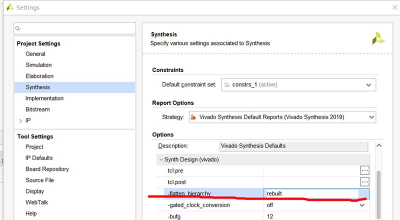

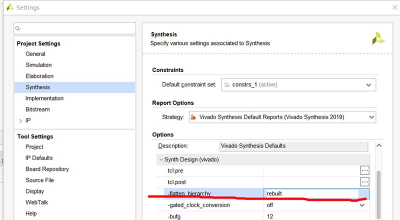

当选择为none,综合器优化的最少,当选择为full时,综合器优化的最多,选择rebuilt时,工具自动选择一个折中的方案,对当前工程做优化。如果在rebuilt的选项不希望一些信号被优化,则可以调用原语进行约束。

当选择为none,综合器优化的最少,当选择为full时,综合器优化的最多,选择rebuilt时,工具自动选择一个折中的方案,对当前工程做优化。如果在rebuilt的选项不希望一些信号被优化,则可以调用原语进行约束。

智能互联设备变得越来越普及,目前全球已经部署了数十亿台智能互联设备。这些智能设备存在于我们的手机、平板电脑、手表、家庭、汽车、城市和云端。在过去,智能设备是指有微控制器,运行某个软件的设备,如今的智能设备则需要执行类人任务。

借助赛灵思Alveo U30媒体加速器卡,亚马逊网络服务(AWS)EC2 VT1实例不仅可加速实时转码,还显著降低了直播视频流的转码成本,从而为高达4K超高清分辨率的多流视频转码提供了最佳性价比。

赛灵思亚太区资深战略应用工程师高亚军将为大家讲解Vivado设计套件,分享其在使用过程中的技巧和设计方法论。

Xilinx Vitis 2020.1里面运行C程序时提示找不到microblaze_0

eFUSE 具备一次性可编程特性,即只要使用特定密钥将“熔丝 (FUSE)”熔断,就无法再使用任何其他密钥对其进行编程。在本文中,我们将探讨有关 AES 密钥验证步骤的内容,当您在器件上以物理方式对 eFUSE 密钥进行编程时应遵循这些验证步骤进行操作。

本文档旨在介绍如何根据 Versal™ ACAP 架构的描述来使用赛灵思的 Xilinx Power Estimator (XPE)。

在Zynq开发时,在Vivado中新建Zynq硬件平台,加入DMA、AXI接口模块,在进行构建软件系统之前,通常需要对硬件平台进行验证,检测模块新建过程中是否存在问题。下面对这一过程进行简单介绍。

在完成“FPGA 功耗”课程之后,您将能够解释静态功耗与动态功耗的区别,描述更小的器件形状对静态功耗的影响,定义泄漏电流与结温的关系,以及描述与功耗相关的某些器件数据手册信息。

Vitis Vision库是OpenCV和Vision功能的加速库,可在Vitis环境中使用,这些库的L1目录是示例设计。为了适应各种用户环境,从2020.1版本开始,Xilinx不再使用Vivado / Vitis工具提供预安装的OpenCV版本。尽管Vitis_hls编译Vision库不需要OpenCV,但是用户测试验证使用时OpenCV。