基于Vitis AI 1.4 实现 Graph Runner 的方法介绍

judy 在 周三, 12/15/2021 - 15:08 提交

本文将重点讲解如何调用 VART API 以运行 XIR 图形。同时,假设我们在处理程序内已有XIR 图形,我们将了解到如何创建runner以及如何在编译流程中启动 graph runner。

本文将重点讲解如何调用 VART API 以运行 XIR 图形。同时,假设我们在处理程序内已有XIR 图形,我们将了解到如何创建runner以及如何在编译流程中启动 graph runner。

Phoronix 报道称,Canonical 预见了 Ubuntu Linux 发行版在 FPGA 领域的光明前景,于是选择与 Xilinx 建立合作伙伴关系。据悉,双方将共同致力于提升“自适应片上系统”(Adaptive SoC)的企业级 Linux 可用性。

如何使用系统调试器查看全局变量?要查看全局变量,请按照以下步骤操作:

昨天,伴随 5G/有线/无线通信专场圆满结束,Xilinx Adapt – 中国站正式落下帷幕。过去的 5 周里,Xilinx Adapt – 中国站围绕 9 大主题,举行了 40 场演讲,覆盖工业、医疗、机器视觉、专业音视频与广播、汽车与自动驾驶、开发者、数据中心以及有线与无线通信。

为了更好地支持参赛者顺利完成比赛和提高效率,我们邀请到了赛灵思国内外的多位软硬件技术工程师与专家,针对3个赛道定向解答。欢迎大家带着问题加入会议或者旁听学习交流开发经验!

由于要满足尽量多的客户需求,Xilinx的默认linux kernel的配置,包含了尽可能多的常用模块。实际嵌入式产品中,很多模块用不到。对于不用的模块,可以配置linux kernel,去掉它们。

Xilinx AI团队核心成员严丹在首届“英特尔创新大师杯”深度学习挑战赛比赛通用场景中文OCR文本识别任务中,通过两阶段网络结构,融合基于分割和基于Mask RCNN的检测模型预测结果,在复赛测试集上获得75.34的高分, 取得冠军。

现在经常会有关于一种新架构的公告,它是由三个字母组成的首字母缩写——TPU, IPU,NPU等。但它们真正的区别是什么呢?是否真的有那么多独特的处理器架构?

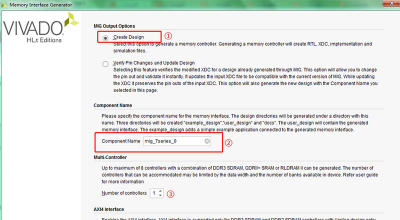

干货来了,用DDR搬砖,只需要会用IP就好,Xilinx官方YYDS!

项目许可证和网站许可证之间的区别是什么?例如,我想决定购买EF-DI-CORE-IP-PROJ(项目许可)还是EF-DI-CORE-IP-SITE(站点许可)?