开发者分享| Vitis_HLS, 玩转AXI总线突发读写的代码风格-上

judy 在 周一, 12/27/2021 - 10:54 提交

在Vitis HLS 工具中,要真正完成AXI总线突发,我们需要一个合适的代码风格并结合恰当的指令设置来达到这个目的。本章节带大家看看如何玩转AXI总线突发读写的代码风格-上。

在Vitis HLS 工具中,要真正完成AXI总线突发,我们需要一个合适的代码风格并结合恰当的指令设置来达到这个目的。本章节带大家看看如何玩转AXI总线突发读写的代码风格-上。

使用Jtag Master调试FPGA程序时用到tcl语言,通过编写tcl脚本,可以实现对FPGA的读写,为调试FPGA程序带来极大的便利,下面对FPGA调试过程中常用的tcl语法进行介绍,并通过tcl读FIFO的例子,说明tcl在实际工程中的应用。

2021自适应计算挑战赛赛程已过半,近期在开发设计过程中,我们收到众多开发者对于硬件板卡的资料查找询问。XILINX开发者社区特此整理了关于3个硬件赛道板卡在项目设计和开发时的时间周期安排与各硬件设计时做需要的资料介绍,希望对大家有所帮助。

本文演示如何使用Vivado® Design Suite创建一个从HDL综合到BIT文件生成的动态功能交换(DFX)设计。通过DFX,您可以对使用中的Xilinx®器件的某些区域进行重新编程和重新使用,同时该器件继续运行。

由于现在Sony的图像传感器靶面越来越大,100M像素以上的也很多;帧率也越来越高,1000fps以上的也不在少数,因此SLVS-EC接口在至少在Sony的Sensor上会用得越来越多。

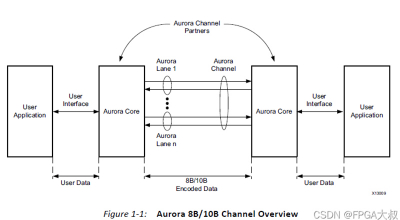

Aurora 广泛用于需要背板、电路板间和芯片间连接的应用。细分市场包括有线通信、存储、服务器、测试测量、工业、消费和医疗等。此外,Aurora 也可用作嵌入式处理器应用中的调试端口。

在STA中,要分析上游器件和FPGA之间的时序关系就得指定input delay。

本文主要介绍基于OpenAMP框架的双核ARM通信案例的使用说明,CPU0(Master)运行Linux系统,CPU1(Remote)运行裸机或FreeRTOS程序。CPU0使用remoteproc加载CPU1程序,并对CPU1进行配置。

为了更好地为2021赛灵思自适应计算挑战赛的参赛者提供赛事支持,由赛灵思团队举办的答疑会 Office Hour #1 已于12.15日完成,我们邀请到了众多Xilinx的软硬件技术工程师与专家,专门针对3个赛道提供软硬件答疑。

VeriTiger-V19P系列基于当前业界单颗芯片最高逻辑密度和最大I/O数量的Xilinx VU19P FPGA,提供VeriTiger-V19P(单片VU19P)、VeriTiger-DV19P(双片VU19P)、VeriTiger-QV19P(四片VU19P)三种硬件形态