【线上活动】Xilinx Adapt China: Vivado

judy 在 周一, 03/29/2021 - 11:40 提交

4月22日-23日,赛灵思举办 Adapt China:Vivado专场,特邀Vivado专家团队,与您分享 Vivado 在设计自动化集成、IP子系统复用和加速设计收敛等方面的方法和技巧。

4月22日-23日,赛灵思举办 Adapt China:Vivado专场,特邀Vivado专家团队,与您分享 Vivado 在设计自动化集成、IP子系统复用和加速设计收敛等方面的方法和技巧。

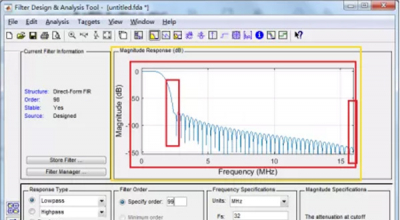

本文以99阶FIR低通滤波器为例,学习使用matlab的fdatool工具箱设计滤波器,并将滤波器系数导出到.coe文件,联合Vivado进行FPGA的FIR滤波器设计

中文版 Parallel Programming for FPGAs(pp4fpgas, FPGA并行编程-以数字信号处理为例)是本公众号最受欢迎的内容之一,中文书稿和开源项目截止目前已有数万的访问量。这本书也是许多不熟悉FPGA的开发者在从PYNQ入门后,进行算法硬件实现的第一本入门宝典

赛灵思Vitis AI开发环境的正确安装姿势

Xilinx自适应器件的灵活性和可配置性与IP和工具产品相结合,可显著提高安全处理性能。

本视频快速介绍 Vitis AI Model Zoo 的计划和内容,包括全新 1.3 版本中的新增功能。

因为 BD 中连线太多,所以想自定义下 interface 简化连线,定义好了一个 interface,但当准备在自定义 IP 中指定它时,发现我把一个信号的方向搞错了,应该定义成 out,但实际定义成了 in,所以想简单的改一下方向。

Alveo 加速卡除了有我们 ultrascale+系列的芯片以外,还有 TI 的 MSP432,它的作用就是监控板子的状态,比如电流电压温度等信息。主控端可以通过 FPGA,访问 MPS432,然后获取这些信息。那么怎么样简单的获得这些信息呢,为此我们准备了 CMSIP。

本视频介绍了Vitis和Vitis-AI,将重点讲解Vitis-AI的设计流程以及如何在边缘和云端器件上进行部署。

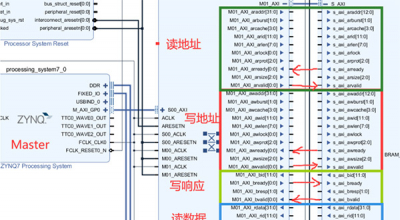

AXI4协议是一个点对点的主从接口协议,数据可以同时在主机(Master)和从机(Slave)之间双向传输,且数据传输大小可以不同。AXI4中的限制是一个突发事务(Burst)最多可以传输256个数据,AXI4-Lite只允许每个事务传输1个数据。