自适应 SoC,让IP音视频传输充满更多可能

judy 在 周三, 03/24/2021 - 15:13 提交

作为音视频行业各种设备制造商的供应商,客户经常会来咨询,我们认为哪一种 IP 音视频传输标准将最终胜出。我们看到广播行业曾经出现过这样的不确定性和混乱时期。当时存在多项相互竞争的协议,竞相角逐同样的应用,造成整个行业在一段时间里踌躇不前,发展停滞。

作为音视频行业各种设备制造商的供应商,客户经常会来咨询,我们认为哪一种 IP 音视频传输标准将最终胜出。我们看到广播行业曾经出现过这样的不确定性和混乱时期。当时存在多项相互竞争的协议,竞相角逐同样的应用,造成整个行业在一段时间里踌躇不前,发展停滞。

在探索宇宙的道路上,无数顶尖的科学家、企业都为之做出了自己的贡献。可以说,人类对宇宙的征途,是所有相关人员、企业的智慧结晶。作为自适应计算的领军者,赛灵思在充满未知的宇宙探索领域,贡献了不可忽视的力量。

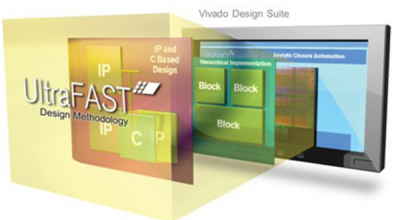

赛灵思 UltraFast™ 设计方法旨在帮助简化当今器件设计进程的最佳实践,帮助用户在 Vivado® Design Suite 中有效利用赛灵思 FPGA 器件资源,并加速完成设计实现和时序收敛提供推荐方法背后的原理,以支持用户制定出明智的设计决策。

具有“工程师的眼睛”美称的示波器,是如今数字时代设计、制造、维修电子设备时不可或缺的工具。它能帮助工程师查看时域和射频域中的各种模拟信号和数字信号、观察高速数字总线的信号完整性或检查电源的电压和电流

赛灵思 Versal ACAP 硬件、IP 和平台开发方法论是旨在帮助精简 Versal 器件设计进程的一整套最佳实践。Versal ACAP从设计之初即采用正确方法并尽早关注设计目标(包括 IP 选择和配置、块连接、RTL、时钟、I/O 接口和 PCB 管脚分配)至关重要。

从 NAND 闪存启动 Zynq-7000 SoC 器件时,BootROM 中的 NAND 驱动在 NAND 参数页面 (Parameter Page) 中执行读取时不会对输入进行验证。如果从参数页面读入的备用字节包含恶意的非法值,则会导致缓冲器上溢,从而可能导致执行任意代码。

一个按一定速度沿x轴行进,同时半径按一定频率在圆周上滑动的圆,最后留下的痕迹就是一个正余弦波。DDS全称直接数字频率合成(Direct Digital Synthesis),简单来讲,分以下几步:

本视频演示了 2020.2 版嵌入式软件工具环境新增功能,其中涵盖了嵌入式软件栈和工具方面的更新与更改。

Xilinx公司采用InFO封装的新型Zynq UltraScale+ MPSoC实现了全方位的工业性能--所有这些器件都采用了具有高计算密度的紧凑外形。

Pass是TVM中基于relay IR进行的优化,目的是去除冗余算子,进行硬件友好的算子转换,最终能够提高硬件运行效率。由tensorflow等深度学习框架生成的图机构中,含有很多可以优化的算子,比如expand_dim,len等,其实在编译阶段完全可以优化掉,从而能够减少硬件的计算,以及避免出现硬件不支持的算子。