【视频】赛灵思 UltraScale+ 成本优化的产品组合

judy 在 周四, 03/18/2021 - 09:45 提交

了解全新的 16nm Artix® UltraScale+™ FPGA 系列和 Zynq® UltraScale+ MPSoC ZU1 器件,以超紧凑的封装提供,可为成本敏感型的边缘和网络应用提供无与伦比的计算密度。

了解全新的 16nm Artix® UltraScale+™ FPGA 系列和 Zynq® UltraScale+ MPSoC ZU1 器件,以超紧凑的封装提供,可为成本敏感型的边缘和网络应用提供无与伦比的计算密度。

本文档旨在描述推荐的设计方法,帮助用户在 Vivado® Design Suite 中有效利用赛灵思 FPGA 器件资源,并加速完成设计实现和时序收敛。提供推荐方法背后的原理,以支持用户制定出明智的设计决策。

一图读懂赛灵思全新UltraScale+成本优化型产品组合

赛灵思今日宣布面向市场扩展其 UltraScale+ 产品组合,以支持需要超紧凑及智能边缘解决方案的新型应用。新款 Artix® 和 Zynq® UltraScale+ 器件的外形尺寸较传统芯片封装缩小了70%,能够满足工业、视觉、医疗、广播、消费、汽车和互联市场等更广泛的应用领域。

身处智能时代,科技发展日新月异,伴随数据中心、有线网络、5G 无线和汽车等愈加丰富的场景,相应的技术与功能也正经历飞速迭代,因此,单一计算架构已难以应对海量数据处理需求,赛灵思 Versal ACAP多核异构计算平台致力于帮助所有开发者保持即时的灵活应变能力。

人工智能的发展、日益复杂的工作负载以及非结构化数据的爆炸式增长,正迫使数据中心快速转型。随着 5G 、人工智能( AI )、云计算、物联网及自动驾驶等新一代信息技术快速演进,全球数据正呈指数级增长并呈海量聚焦态势。

目前ASIC的设计变得越来越大,越来越复杂,单片FPGA已不能满足原型验证要求,多片FPGA验证应运而生。RTL逻辑的分割、多片FPGA之间的互联拓扑结构、I/O分配、高速接口都对应用FPGA原型验证的芯片开发者提出了更高的要求也带来了前所未有的挑战。

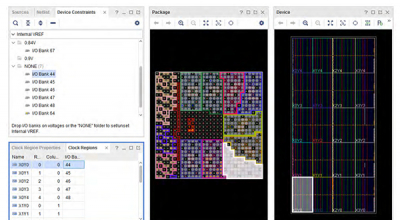

本文描述了I/O规划过程,在RTL设计中与PCB设计人员一起执行端口分配,并与系统工程师一起利用目标Xilinx FPGA上的时钟资源;使用Vivado设计套件减少内部和外部导线长度,提高系统性能。

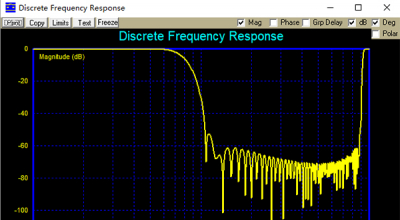

我们上一篇文章的混频是8MHz与5MHz的相乘,所以我们这篇文章的目的是设计一个低通滤波器滤除13MHz的成分。FIR的设计方法在数字信号处理中有两种方法,最常用的就是窗函数法。这里我们将使用汉明窗进行进一步的设计。

vivado提供了DDS IP核可以输出正余弦波形,配置方法如下