TVM学习(八)pass总结

judy 在 周一, 03/22/2021 - 10:06 提交

Pass是TVM中基于relay IR进行的优化,目的是去除冗余算子,进行硬件友好的算子转换,最终能够提高硬件运行效率。由tensorflow等深度学习框架生成的图机构中,含有很多可以优化的算子,比如expand_dim,len等,其实在编译阶段完全可以优化掉,从而能够减少硬件的计算,以及避免出现硬件不支持的算子。

Pass是TVM中基于relay IR进行的优化,目的是去除冗余算子,进行硬件友好的算子转换,最终能够提高硬件运行效率。由tensorflow等深度学习框架生成的图机构中,含有很多可以优化的算子,比如expand_dim,len等,其实在编译阶段完全可以优化掉,从而能够减少硬件的计算,以及避免出现硬件不支持的算子。

本视频着重介绍了 Vivado Design Suite 2020.2 版中的新增功能,包括操作系统和器件支持、高级别增强功能以及加速设计集成、实现与验证相关的各项改进措施。

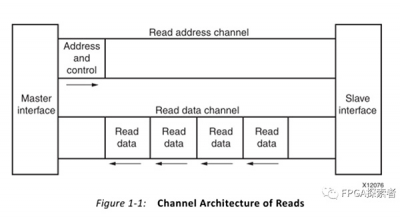

AMBA® AXI4(高级可扩展接口 4)是 ARM® 推出的第四代 AMBA 接口规范,AMBA(Advanced Microcontroller Bus Architecture)是片上总线标准,包含AHB(Advanced High-performance Bus)、ASB(Advanced System Bus)和 APB(Advanced Peripheral Bus)。

今天邀请到赛灵思专家和大家分享下如何在 Petalinux 下定位 decice-tree 错误的一些技巧。

赛灵思应用商店 (Xilinx App Store) 是赛灵思首次面向广大用户所提供的数字化自适应加速应用发布平台,其加速应用来自赛灵思、第三方合作伙伴和优质独立软件开发商。目前,Xilinx 应用商店支持多种领域的加速计算,包括视频及图像处理、数据分析、高性能计算、机器学习及网络安全等

您所不知道的 Xilinx:深耕汽车市场 20 年的故事

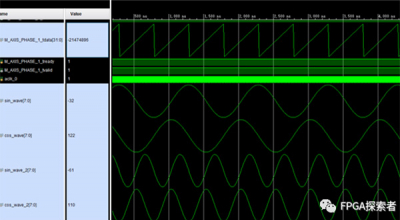

本次使用Vivado调用DDS的IP进行仿真,并尝试多种配置方式的区别,设计单通道信号发生器(固定频率)、Verilog查表法实现DDS、AM调制解调、DSB调制解调、可编程控制的信号发生器(调频调相)。

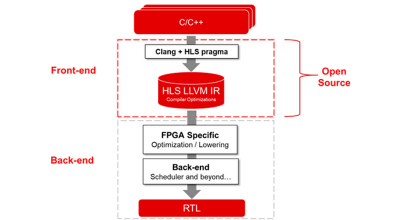

赛灵思一直致力于支持开源计划的不断飞跃,为帮助开发人员和研发社区充分发挥自适应计算的优势,我们再次做出了令人振奋的举措: 在 GitHub 上开放提供 Vitis HLS(高层次综合)前端。Vitis HLS 工具能够将 C++ 和 OpenCL™ 功能部署到器件的逻辑结构和 RAM/DSP 块上。

随着技术的发展与革新,服务器、SmartNIC与DPU之间的界限越来越模糊,但实际上,定义与用例之间几乎没有多大关系。今天,我们针对Xilinx日前推出的新一代Alveo SmartNIC产品组合,从中窥探SmartNIC的未来发展趋势:可组合性。

了解全新的 16nm Artix® UltraScale+™ FPGA 系列和 Zynq® UltraScale+ MPSoC ZU1 器件,以超紧凑的封装提供,可为成本敏感型的边缘和网络应用提供无与伦比的计算密度。