2020 人工智能卓越创新奖,请为 Xilinx 打 call

judy 在 周三, 05/27/2020 - 09:34 提交

《电子发烧友》2020 “中国人工智能卓越创新奖”评选重磅登场,赛灵思及其两大平台同时入选提名!

《电子发烧友》2020 “中国人工智能卓越创新奖”评选重磅登场,赛灵思及其两大平台同时入选提名!

随着赛灵思 Alveo 自适应计算加速卡的发布,数据中心各种工作负载开启了自适应计算加速的历程。本期小编特整理了有关 Alveo 的一批中文文档,以供各位随时下载和查阅。

本次网络研讨会描述了两个使用 Zynq UltraScale + RFSoC 进行无线通信的设计示例。 首先,让我们回顾一下针对大规模 MIMO(64x64),100MHz LTE(ORAN 7.2 split)的设计,并解释其实现和选型性能数据。

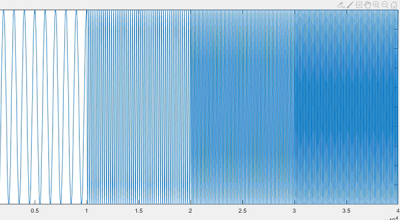

在Matlab中,做短时傅里叶变换需要使用函数spectrogram,而在Matlab2019中,引入了一个新的函数stft,下面我们就来看下这两个函数都如何使用。

首先通过上面的简单分析,我们应该很清楚一件事:TCP协议很复杂,光握手过程就需要“三次握手、四次挥手”的复杂过程,不是特别适合FPGA的纯逻辑实现,因为用FPGA实现以太网通信的主要目的就是进行低延时的传输数据,而一旦设计规模达到一定量级,FPGA实现通信的优势便不复存在,转而体现出“性价比”低的劣势

数字信号对载波信号的振幅调制称为振幅键控,即ASK。在2ASK调制系统中,数字信息只有0和1两种,所调制的载波信号的幅度变化状态也只有两种:无载波输出时代表发送0;有载波输出时代表发送1。在4ASK调制系统中,数字信息就有00、01、10、11四种,需要载波信号幅度的4个电平状态表示

在数据指数级增长对智能化、灵活应变的网络和数据中心解决方案提出极高要求的今天,全新 Virtex UltraScale+ VU23P FPGA 为行业提供了所需的最大吞吐量、强大的数据处理能力以及灵活性优势,使其可以适应不断演进发展的连接标准,并满足当前与未来需求

随着高带宽内存(HBM)的发展,FPGA正变得越来越强大,HBM 给了FPGA 更多能力去缓解再一些应用中遇到的内存带宽瓶颈和处理更多样的应用。然而,HBM 的性能表现我们了解地还不是特别精准,尤其是在 FPGA 平台上。这篇文章我们将会在HBM 的说明书和它的实际表现之间建立起桥梁

Xilinx的开发板ZCU102支持休眠到内存(suspend-to-ram)。休眠到内存时,DDR进入自刷新,MPSoC被关电,完全不耗电。唤醒时,MPSoC根据外部输入信号判断出不是上电启动而是休眠,就从DDR读出系统状态,恢复系统

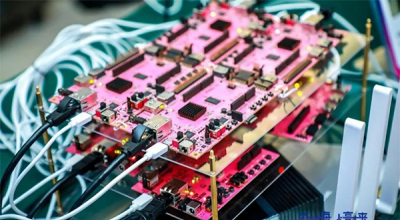

本案例来源于第三届全国大学生FPGA创新设计竞赛中江南大学的OpenHEC lab团队,他们的作品基于PYNQ开源软件框架。PYNQ框架提供了完整的访问FPGA资源的Python library,通过高层次的封装,让开发者通过Python API就可以轻松调用FPGA内的模块或算法,加速产品开发部署