FFShark-一种可以监控全世界网络的100G可编程智能NIC

judy 在 周三, 05/20/2020 - 09:34 提交

本文介绍了Wireshark的快速FPGA实现FFShark。其结果是一个紧凑的、相对便宜的直通设备,可以插入任何正在运行的100G网络中。数据包将在FFShark中传输,不会中断,并且附加的延迟最小

本文介绍了Wireshark的快速FPGA实现FFShark。其结果是一个紧凑的、相对便宜的直通设备,可以插入任何正在运行的100G网络中。数据包将在FFShark中传输,不会中断,并且附加的延迟最小

Vivado 集成设计环境支持将通用验证方法学 (UVM) 应用于Vivado 仿真器。Vivado 提供了预编译的 UVM V1.2 库。请遵循以下步骤创建示例设计测试案例,以便在工程模式下使用 UVM。本文随附了 1 个简单示例,可供您下载解压使用。

调制就是把要传递的信号“搬运”到规定的频率附近,从技术上说,天线的尺寸和电磁波的波长差不多的时候,才能获得较高的发射效率,假设信号是10MHz,那么波长为30m,这么长的天线显然是不现实的。因此需要把信号调制到较高的频率,减少天线的尺寸

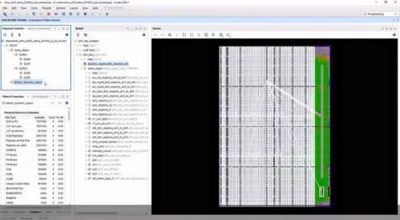

本视频解读 DFX 布局规划基本信息视频,介绍了扩展布线区域的使用。这项 Vivado 功能面向 UltraScale 和 Ultrascale+ 器件,可改善 DFX 设计结果,设计人员创建其布局规划时应考量如何运用此功能

本周,IBM声称,其神经计算机系统达到了每秒120万帧的训练时间,创下了最新记录。IBM在AI模型训练上实现了大突破,可与最先进的技术相匹敌。网友对此表示简直不敢相信!

上期我们分享了王伟老师的 技术文章解析(上),本期将会给大家带来下集解析,Ultra96v2petalinux 2019.2软件平台设计与调试和Vitis AI Linux加速平台的介绍。

作者:付汉杰,hankf@xilinx.com,文章转载自:博客园

本视频围绕 UltraScale 和 UltraScale+ 架构,回顾了 DFX 布局规划基本信息;并提供了通过创建更优化的布局规划来改善设计结果的策略和技巧。

在仿真验证中,SV语言不能很好的描述复杂的计算或者流程关系,使用软件语言(比如C)就比较方便。那么当我们使用C描述了这些关系后,如何在基于SV的仿真环境中使用呢?有两种方式,一种是将C编译为可执行文件,利用系统函数进行调用。另

各位开发者小伙伴请听题:

请问,Vitis 从入门到实践需要几步?

这个过程比大家想象中简单

答案是:只需四“部”

为什么是四“部”?

答案马上揭晓