【干货分享】运行EGL Pixmap例子,测试MPSoC GPU性能

judy 在 周二, 05/12/2020 - 16:34 提交

作者:付汉杰,hankf@xilinx.com,文章转载自:

作者:付汉杰,hankf@xilinx.com,文章转载自:

该演示说明了如何使用 Vitis™ IDE 进行软件性能分析。

随着现代图像及视频处理技术的不断发展,人们对图像处理提出了新的要求,最近几年,图像的分辨率和扫描频率都有了较大范围的提升,1080P分辨率的视频已经非常流行,2K甚至4K分辨率的图像也在火热发展中。基于软件的图像处理方法存在着一些局限性,尤其是计算速度和算法效率方面

心跳包就是在客户端和服务器间定时通知对方自己状态的一个自己定义的命令字,按照一定的时间间隔发送,类似于心跳,所以叫做心跳包。心跳包在GPRS通信和CDMA通信的应用方面使用非常广泛。数据网关会定时清理没有数据的路由,心跳包通常设定在30-40秒之间。所谓的心跳包就是客户端定时发送简单的信息给服务器端告诉它我还在而已

该演示将指导用户完成使用 Vitis™IDE 创建和执行 Linux 应用程序所涉及的步骤。

本案例支持CameraLink Base/Full模式、彩色/黑白相机。 此开发详解基于创龙ZYNQ Z-7045/Z-7100评估板TLZ7xH-EVM展开。

随着人工智能和5G的兴起,数据处理对芯片的算力和带宽要求更高。为了布局未来,助力人工智能和5G,赛灵思也推出了自己的FPGA加速芯片-ACAP。ACAP是一款基于7nm工艺,集成了通用处理器(PS),FPGA(PL),math engine以及network-on-chip的革命性芯片。

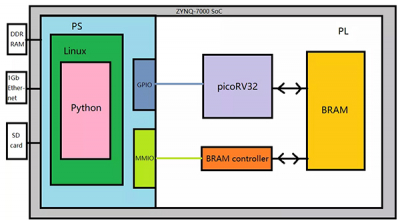

RISC-V-On-PYNQ Overlay实现了在PYNQ-Z2板上的RISC-V处理器及工具链集成,并提供了完整的RISC-V源码与设计流程,得益于PYNQ软件框架,其支持在Jupyter Notebook对RISC-V进行编译、调试与验证,即可以在Jupyter Notebook上编写一段C/C++/RISC-V汇编程序,将编译后的二进制文件放到picoRV32上运行

本篇博文涵盖了配置设备树以将外设和第三方应用详细信息添加到 PetaLinux 工程中的基本流程。在某些情况下,设备树无法生成相关外设所需的所有必需信息,例如,以太网 PHY 信息。在此类情况下,您需要手动将此板级信息和特定开发板信息添加到设备树文件 (system-user.dtsi) 中。

成为公民科学家不是梦!闲置的计算资源不仅用于精确地建模重要蛋白质的结构,还用于设计新蛋白质,让我们一起参与抗击COVID-19!