Modelsim的简单使用

judy 在 周四, 04/30/2020 - 09:21 提交

对于FPGA开发而言,仿真是开发流程中必不可少的一步,也是非常重要的一步,仿真是将RTL代码模拟运行,得到module中信号波形,再进行功能分析的过程。强大的功能与速度兼具的modelsim仿真就是你开发过程的最合适的选择了,下面我以简单的24进制计数器带各位熟悉modelsim仿真流程及波形

对于FPGA开发而言,仿真是开发流程中必不可少的一步,也是非常重要的一步,仿真是将RTL代码模拟运行,得到module中信号波形,再进行功能分析的过程。强大的功能与速度兼具的modelsim仿真就是你开发过程的最合适的选择了,下面我以简单的24进制计数器带各位熟悉modelsim仿真流程及波形

现场可编程门阵列 (FPGA) 具有诸多特性,无论是单独使用,抑或采用多样化架构,皆可作为宝贵的计算资产;但是许多设计人员并不熟悉 FPGA,亦不清楚如何将这类器件整合到设计中。解决办法之一是深入研究主要供应商提供的 FPGA 架构及相关工具;本文则从 Xilinx 产品系列开始着手

本文描述了为实现深度学习神经网络推理应用程序中的矩阵乘法加速而设计的大型乘法脉动阵列的实现和评估。

有两种方法可以将 Alveo 数据中心加速卡上 Quad SPI 部件的内容还原为出厂映像。 本答复提供一般性说明,以及带逐步说明的文档的参考。

本篇介绍AXI4-Lite接口协议的数据读写操作~

有些应用中,单板没有DDR,OCM又不够存储所有数据和指令。这种情况下,Xilinx提供了参考设计Zynq-7000 AP SoC Boot - Booting and Running Without External Memory,把代码和只读数据放在QSPI Flash中运行程序,这就是execute in place (XIP)。

数字下变频是一种广泛应用于数字无线电接收机的数字信号处理技术,其主要目的是经过数字混频将A/D转换输出的中频信号搬移至基带,然后通过滤波,抽取完成信道提取的任务,主要的电路模块由四部分组成:数控震荡、数字混频、数字滤波、采样抽取。

终于到了今天的猪脚-SerDes,为什么拿SGMII和SerDes进行对比,主要原因是,SerDes是一个串行接口,和SGMII很像,和GMII几乎没有什么交集,所以两者对比就没有什么实际意义,所以只进行SGMII和SerDes进行对比。

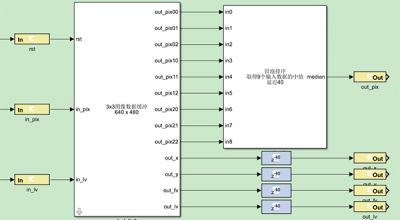

中值滤波是一种算法简单,效果较好的“高性价比”去噪算法。算法原理是使用图像内二维滑窗的中值(全部像素点数值排序位于中间位置的数值为中值)代替当前像素点值。如下图的 3×3滑窗内,处于滑窗中心的当前像素点值为 8,滑窗内全部 9 个像素点的中值为 5

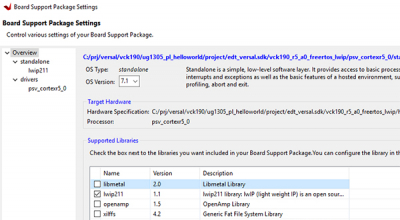

Xilinx的SoC在业界应用非常广泛。对应的开发工具SDK也很成熟。在SDK里,每一个baremetal工程,对应一个BSP工程,它包含一些Xilinx提供的公共模块,比如硬件的驱动、freertos、LWIP等。在BSP工程的右键菜单中,选择BSP setting,可以配置BSP工程包含的的公共模块。