千兆以太网(1):接收——RGMII协议和IDDR原语

judy 在 周五, 04/24/2020 - 10:15 提交

电脑上位机将一幅 1024*768 图片通过双绞线(网线),发送给板卡网口(RJ45接口),RJ45接口将数据传输给网卡(PHY芯片),PHY 芯片将差分信号转换成双沿数据,IDDR将双沿数据转换成单沿数据传输给 FPGA

电脑上位机将一幅 1024*768 图片通过双绞线(网线),发送给板卡网口(RJ45接口),RJ45接口将数据传输给网卡(PHY芯片),PHY 芯片将差分信号转换成双沿数据,IDDR将双沿数据转换成单沿数据传输给 FPGA

PetaLinux环境下,也可以使用Yocto/openembedded的bitbake。Xilinx ug1144有详细说明。为了方便,我编写了以下脚本,导入bitbake需要的环境。将下列脚本保存为sh文件,使用source导入,之后就能使用bitbake。脚本的第一个输入参数是PetaLinux版本号,比如2019.2。

Versal Premium ACAP能够以最小功耗和占板面积在灵活应变的平台上实现突破性异构集成,以及超高性能计算、连接与安全功能。本白皮书将介绍Versal Premium ACAP的独有特性,对一些精心挑选的用例进行回顾,并概述这种集成软硬平台为软硬开发者和数据科学家带来的优势。

在本文中,您将了解有关内部集成电路总线(I2C 或 IIC)的基础知识以及将此协议总线应用于短距离通信的方法。I2C 属于串行通信协议,供双线接口用于连接 EEPROM、传感器、RTC、ADC/DAC 等低速器件以及嵌入式系统中的其它兼容 I/O 接口。

在我们所有人的生活和工作因疫情陷入困顿之际,鼓舞我们大多数人继续前行的力量来自于社会与企业合作的一个又一个鲜活的抗疫案例,他们通过各种各样的技术和创新解决方案,助力抗击新冠疫情。

ThunderImage 是深维科技的旗舰级产品,它基于赛灵思 Alveo 加速器卡进行图像处理加速。利用 ThunderImage,数据中心用户可以将图像处理性能提高多达 20 倍,延迟降低 5 倍,同时 QoS 却保持不变,电源效率提高了 10 倍,TCO 降低了 5 倍

被世卫组织称为全球性“大流行”的新冠肺炎疫情,正以每天数万人确诊的速度急遽攻城略地,医疗用品和医疗设备的严重短缺已经成为抗击病毒一线最迫切的难题。在这样一场全球浩劫当中,任何人的任何努力都将为打败这场“疫情”提供助力

了解 Xilinx HLS 技术如何使用可移植的 C 代码提取和实现任务并行。

本视频基于 developer.xilinx.com 上推出的文章

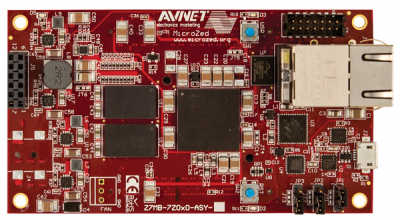

Vitis是Xilinx新推出的统一软件平台,可实现在 Xilinx 所有芯片(包括 FPGA、SoC 和 Versal ACAP)上开发嵌入式软件和加速应用。Xilinx主要宣传Vitis可以为异构平台的应用实现加速。其实,Vitis也能完美的支持嵌入式软件开发。下面以MicroZed单板为例,介绍在Vitis里如何创建嵌入式软件工程,并且编译和调试,直到启动。

一直想移植高版本的ubuntu系统,但都是文本终端的,安装桌面操作总是出问题,没办法折腾一顿只能回来安装网上常用的12版本的。