Zynq中PS的MIO操作

demi 在 周三, 01/08/2020 - 19:19 提交

GPIO有4个BANK,注意与MIO的BANK区分。BANK0控制32个信号,BANK1控制22个信号,总共是MIO的54个引脚,BANK2和BANK3共能控制64个PL端引脚,每一组都有三个信号,输入EMIOGPIOI,输出EMIOGPIOO,输出使能EMIOGPIOTN,共192个信号。

GPIO有4个BANK,注意与MIO的BANK区分。BANK0控制32个信号,BANK1控制22个信号,总共是MIO的54个引脚,BANK2和BANK3共能控制64个PL端引脚,每一组都有三个信号,输入EMIOGPIOI,输出EMIOGPIOO,输出使能EMIOGPIOTN,共192个信号。

Xilinx对Clock的管理如分频,倍频等没有使用IP,而是直接调用了相关原语MMCME3_ADV,在这里MMCME3_ADV原语是针对UltraScale的器件的,7系列的器件相关原语名称为MMCME2_ADV。这个规则和LVDS的serdes等原语一致。

有了这么多的灵活性,我们如何利用Xilinx统一软件工具的所有功能来最好地应对应用程序挑战? 在本课程中,我们将研究这些工具适用于所有三个不同的工作流程:AI引擎软件开发,传统的仅CPU的软件开发和硬件加速。

准则1:合适的代码风格

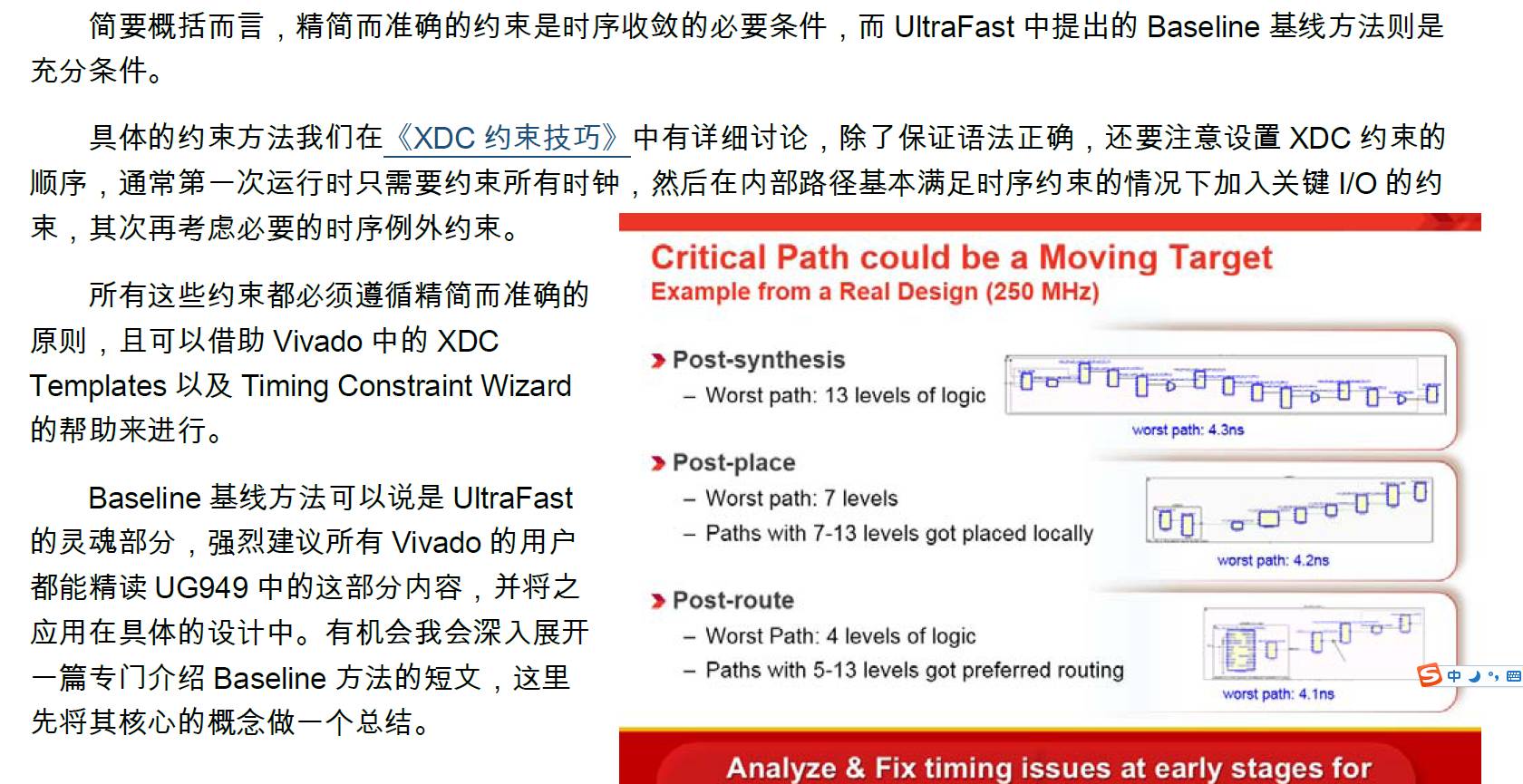

准则2:精准的时序约束

准则3:管理高扇出网络

准则4:层次化设计结构

创建特定于域的体系结构的能力是Xilinx设备的主要优势,但不要只局限于应用程序的一个方面!在本次会议中,我们将讨论Vitis的端到端应用程序加速潜力,包括AI流程以及使用Xilinx硬件加速的Vitis库的复杂系统的组成。

随着人工智能和物联网技术的融合,AIoT(人工智能物联网)的概念应运而生,即AI(人工智能)+IoT(物联网)。目前,边缘AI正广泛应用于工业领域,这种技术可以为工业物联网边缘的多传感器分析和机器学习应用提供最低的时延、功耗和成本。在工业领域,当前热门的边缘AI应用包括工业机器人、智慧路灯、智能监控等。

对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和异步复位没有区别,当然由于器件内部信号均为高有效,因此推荐使用高有效的控制信号,最好使用高有效的同步复位。输入复位信号的低有效在顶层放置反相器可以被吸收到IOB中。

今天跟大家分享的内容很重要,也是我们调试FPGA经验的总结。随着FPGA对时序和性能的要求越来越高,高频率、大位宽的设计越来越多。在调试这些FPGA样机时,需要从写代码时就要小心谨慎,否则写出来的代码可能无法满足时序要求。

5G 商用浪潮正席卷全球。相关调查显示,截止 2019 年 11 月,全球已共有 21 个国家的 43 家运营商开始提供已商用 5G服务,另有 77 家运营商正在规划中计划商用。与此同时,截至 2019 年第三季度,全球5G连接已经达到共有约 488 万。