【视频】采用 FPGA 技术降低 4G/5G 基站的功耗、尺寸和制造成本

judy 在 周一, 04/27/2020 - 10:07 提交

使用可编程硬件技术来实现完整的发射链,以提高功率放大器的效率,通过可编程硬件技术实现完整的接收链,其中包括数字下变频以及与模拟前端和无线电设备控制器连接的接口。

使用可编程硬件技术来实现完整的发射链,以提高功率放大器的效率,通过可编程硬件技术实现完整的接收链,其中包括数字下变频以及与模拟前端和无线电设备控制器连接的接口。

很多工程师都会选择多个jobs进行编译,以为这样会更快一些,而且这个jobs的数量跟本地CPU的线程数是一致的,这就更加让工程师们认为这个选项就是多线程编译了。但对Vivado更加熟悉的工程师,肯定会知道,Vivado中的多线程是通过tcl脚本去设置的,而且目前最大可使用的线程数是8个,那这个jobs跟多线程有什么关系呢?

前面我们实现了FPGA板卡接收以太网的数据,但是里面的数据比较乱,而且可能出现无效帧,即便是有效帧,也不是所有数据都是我们要的,必须对数据进行筛选。本篇博客详细记录一下以太网数据的校验和筛选。

某些应用程序小,可以全部放在Zynq-7000的256KB OCM上运行。这时,修改FSBL,可以把APP和FSBL编译成一个可执行文件,FSBL初始化硬件后,就直接运行应用程序。这种情况下,单板没有DDR。

本设计咨询主要面向 7 系列和 Virtex-6 FPGA,其中包含赛灵思针对 2020 年 4 月 15 日发布的一篇有关破解比特流加密的文章的回应,详情将于“USENIX Security 2020”大会上发表

“人们常说眼睛是心灵的窗户,带着你我看清现实世界。”在工业发展中,工业智能化替代了人类的手脚,而机器视觉就是智能化的眼睛,让其更精准的解决工业场景需求。同时智能化物联网时代不断发展的今天对机器视觉产生了更高的要求。

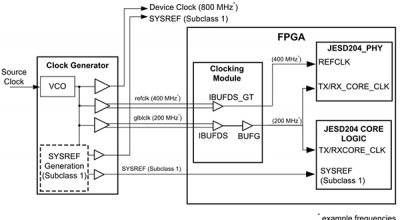

本篇参考xilinx官方JESD204 IP核的数据手册PG066,具体介绍基于该IP核的JESD204B数据传输实现方法~

图像处理算法在各种场景中都有广泛应用,借助于FPGA并行计算的优势可以将算法性能有效提升,但为了提升系统整体性能,仅仅提升某一部分的性能是不够的,一个好的方法是在FPGA内实现全部视频输入输出接口和图像算法的完整通路

2011年,德国鲁尔大学的两位博士花了3000美元和7个小时成功破解了Mifare DESFire MF3ICD40使用的安全算法,但这个破解在现实生活却没有任何价值,因为一颗RFID芯片的价值只有几分钱,没人傻到去花大钱去破解一个几乎免费的芯片

通过视频了解如何使用 Xilinx SDK 创建 Linux 应用 。我们还将介绍和演示 SDK 特性 - 支持 Linux 应用开发和调试的全过程。过程快速简便。