上“云”全面加速,FPGA 如何拯救并解放 CPU ?

demi 在 周四, 02/20/2020 - 12:26 提交

以物联网、5G 为核心特征的数字化浪潮正席卷全球,由此带来的车联网、工业物联网、人工智能生物识别带来的海量异构化数据,以及高带宽、低时延等新业务个性化需求,让传统的通用服务器及存储架构不堪重负。

以物联网、5G 为核心特征的数字化浪潮正席卷全球,由此带来的车联网、工业物联网、人工智能生物识别带来的海量异构化数据,以及高带宽、低时延等新业务个性化需求,让传统的通用服务器及存储架构不堪重负。

今天我们要展示的是上海广策信息技术有限公司。其TacFeed和TacMars,目前已经遍布中国各大交易所,包括上交所、深交所、上期所、大商所以及CME等等。这些产品采用了硬件和软件结合的设计方法,大量采用了赛灵思软硬皆可编程的FPGA 自适应计算加速技术,致力于为客户节约每一个纳秒的延迟。

随着物联网的发展和互联设备的不断普及,开发有竞争力的物联网解决方案的最大难题之一就是:将 “智能” 引入边缘设备。

wire 和reg是Verilog程序里的常见的两种变量类型,他们都是构成verilog程序逻辑最基本的元素。正确掌握两者的使用方法是写好verilog程序的前提。但同时,因为他们在大多数编程语言中不存在,很多新接触verilog语言的人并不能很清楚的区别两种变量的不同之处。这里简单对他们做一个比较,方便在编程时区别使用。

同相位时钟可以频率不同,但是时钟跳变沿是对齐的。如图所示,clk0为慢时钟,clk1为快时钟,clk0的时钟沿始终与clk1的时钟沿对齐,两个时钟相位相同。同源时钟,通常由一个PLL或者DLL产生,相位不需要相同,只要求相位固定。

本文主要介绍数字-模拟编码技术。数字 - 模拟编码技术主要有以下几种:

幅移键控编码(ASK,Amplitude shift keying)

频移键控编码(FSK,Frequency shift keying)

相移键控编码(PSK,Phase shift keying)

正交调幅编码(QAM,Quadrature Amplitude Modulation)

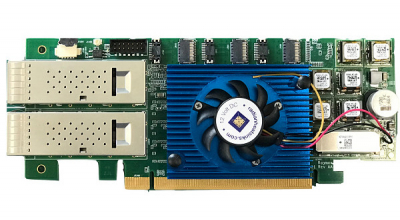

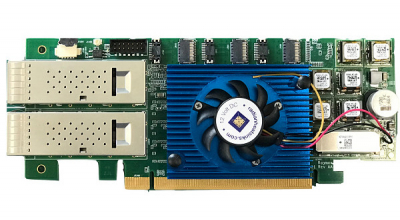

赛灵思 Alveo™ U200/U250 数据中心加速器卡属于围绕赛灵思 Virtex® UltraScale+™ 技术设计制造的外围部件互连高速 (PCIe®) Gen3 x16 兼容卡。这些卡可加速计算密集型应用,如机器学习、数据分析、视频处理等。

时钟树不仅可以做到高扇出,还可以做到让时钟信号到达各个触发器的时刻尽可能一致,也即保证时钟信号到达时钟域内不同触发器的时间差最小。这篇博文进一步说时钟树的问题,我们知道了时钟树的这么强大的功能,好处这么多,那么怎么使用时钟树,我什么时候使用到了时钟树呢?

增量编译对于电路设计之后的调试非常重要,每次也许只修改了一行代码,改了某个值,如果没有增量编译,就只能重新跑一边项目,对于小项目貌似没有太大影响,但是对于一个大项目,每次改一点内容就要重新进行一遍综合,实现,生成比特流,这个过程及其浪费时间,所以增量编译是很必要的。

Vitis AI库是一组高级库和API,旨在通过深度学习处理器单元(DPU)进行有效的AI推理。 它基于具有统一API的Vitis AI Runtime构建,并且完全支持XRT 2019.2。