浮点数基础

demi 在 周二, 02/18/2020 - 12:18 提交

浮点数,是属于有理数中某特定子集的数的数字表示,在计算机中用以近似表示任意某个实数。具体的说,这个实数由一个整数或定点数(即尾数)乘以某个基数(计算机中通常是2)的整数次幂得到,这种表示方法类似于基数为10的科学计数法。

浮点数,是属于有理数中某特定子集的数的数字表示,在计算机中用以近似表示任意某个实数。具体的说,这个实数由一个整数或定点数(即尾数)乘以某个基数(计算机中通常是2)的整数次幂得到,这种表示方法类似于基数为10的科学计数法。

本文主要介绍数字-数字编码中的双极性码。双极性码是使用两个以上的电平值进行编码,无线路信号代表一种信号逻辑状态,正电平和负电平交替代表另一种状态。

本系列文章主要针对FPGA初学者编写,包括FPGA的模块书写、基础语法、状态机、RAM、UART、SPI、VGA、以及功能验证等。将每一个知识点作为一个章节进行讲解,旨在更快速的提升初学者在FPGA开发方面的能力,每一个章节中都有针对性的代码书写以及代码的讲解,可作为读者参考。

为了改进系统同步接口中时钟频率受限的弊端,一种针对高速I/O的同步时序接口应运而生,在发送端将数据和时钟同步传输,在接收端用时钟沿脉冲来对数据进行锁存,重新使数据与时钟同步,这种电路就是源同步接口电路(Source Synchronous Interface)。

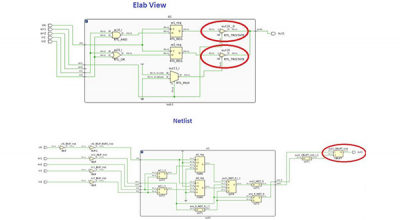

多重驱动定义:具有两个或更多个源的网络或信号被称为多重驱动场景。为何需要解决多重驱动场景?多重驱动的存在属于设计错误,最终值可能难以确定。

如何设计高效的 PL 和 PS 数据交互通路是 ZYNQ 芯片设计的重中之重。AXI 全称 Advanced eXtensible Interface,是 Xilinx 从 6 系列的 FPGA 开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。

通用异步收发传输器(Universal Asynchronous Receiver/Transmitter),通常称作UATR,是一种异步收发传输器。将数据由串行通信与并行通信间做传输转换,作为并行输入称为串行输出的芯片。UART是一种通用串行数据总线,用于异步通信。该总线双向通信,可以实现全双工传输和接收。

本用户指南概述了如何与Vivado®Design Suite一起使用,以创建用于对Xilinx®器件进行编程的新设计。 它简要介绍了各种使用模型,设计功能和工具选项,包括准备,实施和管理设计源和知识产权(IP)核心。

极性码采用两个电压值编码:正电平代表一种信号逻辑状态,负电平代表另一种状态。极性码包括:归零码、不归零码、双相位码、块编码等。

Vivado设计套件有两个主要使用模型:项目模式和非项目模式。 可以通过Vivado IDE或通过Tcl命令和批处理脚本开发和使用项目模式和非项目模式。