【视频】Versal 生命的证据:Hello World

judy 在 周四, 06/27/2019 - 16:13 提交

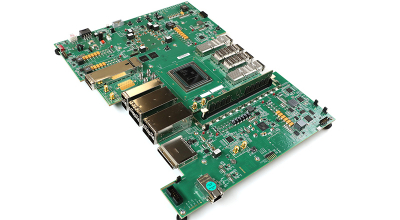

共同见证 Versal™ 向世界发出的第一句话,“Hello World”。这是一个具有非凡意义的一句话,我们将之称为“生命的证据”,从此标志着 Versal ACAP 正式诞生。从收到第一块电路板起,Arm® Cortex®-A72 和 Arm® Cortex®-R5F 在 3 小时内完成启动,而 ARM Cortex-A72 上的 Linux 也在 4 天内完成启动

共同见证 Versal™ 向世界发出的第一句话,“Hello World”。这是一个具有非凡意义的一句话,我们将之称为“生命的证据”,从此标志着 Versal ACAP 正式诞生。从收到第一块电路板起,Arm® Cortex®-A72 和 Arm® Cortex®-R5F 在 3 小时内完成启动,而 ARM Cortex-A72 上的 Linux 也在 4 天内完成启动

本文从最原始文件搭建仿真环境的思路出发,尝试着研究脱离Vivado单独建仿真环境的过程中都会遇到什么问题,采用什么样的方法比较容易解决,笔者试了好几个工程,总结出一套相对完善的解决思路,来分享给大家。

现代高速模数转换器(ADC)已经实现了射频(RF)信号的直接采样,因而在许多情况下均无需进行混频,同时也提高了系统的灵活性和功能。本系列文章将从三个部分入手,说明如何将散射参数(也称为S参数)应用于直接射频采样结构的设计。

工业物联网推动工业控制器从预定义任务自动化向在更大网络中提供灵活节点的概念的发展,其可适应不断变化的任务。可访问更多的信息并可产生更多的数据。这需要将高处理性能与和所用通信协议有关的可扩展网络及灵活性相结合

Xilinx AI SDK是建立在深神经网络开发工具包(DNNDK)和深学习处理器(DPU)之上的一组高级库。通过将大量高效高质量的神经网络封装在DNNDK中,提供了一种简单易用的统一的接口,使用户在没有深度学习知识和FPGA知识的情况下使用深度学习神经网络变得容易

前3篇咱们介绍了 SelectIO 逻辑资源,本篇咱们就聊一聊与SelectIO 逻辑资源水乳交融、相得益彰的另一个概念——IO_FIFO。1个IO_FIFO包括1个IN_FIFO 和1个OUT_FIFO,它是7系列FPGA新设计的IO专用FIFO,主要用于IOLOGIC(例如ISERDES、IDDR、OSERDES或ODDR)逻辑功能的扩展。

体验首款 Versal™ ACAP 芯片从台积电向硅谷赛灵思总部提前交货的旅程,多年耕耘终成伟业。

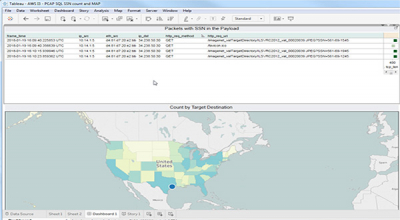

超负荷搜索功能现呈现大数据相关性。BlackLynx 技术将高性能计算(加速的 CPU 和 FPGA)与标准接口及协议相结合,实现高性能分析。

VCU129 开发板整合了集成 PAM4 收发器的 Virtex® UltraScale+™ 58G PAM4 VU29P FPGA,可实现新一代网络平台。VCU129 评估套件展示了 Xilinx SerDes 技术的领先地位,可充分利用 Xilinx 无盖封装方法的低成本散热设计。VCU129 具有多种通用高速互连、板载内存和 PCIe®Gen 3 接口。

在项目中,CERN研究人员通过将AI推理和性能关键传感器的预处理在部署于大型强子对撞机(LHC)中的Xilinx Virtex Ultrascale FPGA上结合,通过自行设计的一套HLS4ML的软件工具,可定制计算极大的加速了处理能力, 并且使得神经网络推理的延时降低到100ns数量级