【视频】Versal ACAP:业界首颗 ACAP 芯片之旅

judy 在 周三, 06/26/2019 - 09:26 提交

体验首款 Versal™ ACAP 芯片从台积电向硅谷赛灵思总部提前交货的旅程,多年耕耘终成伟业。

体验首款 Versal™ ACAP 芯片从台积电向硅谷赛灵思总部提前交货的旅程,多年耕耘终成伟业。

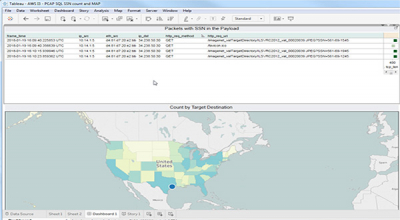

超负荷搜索功能现呈现大数据相关性。BlackLynx 技术将高性能计算(加速的 CPU 和 FPGA)与标准接口及协议相结合,实现高性能分析。

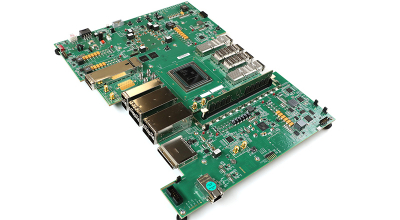

VCU129 开发板整合了集成 PAM4 收发器的 Virtex® UltraScale+™ 58G PAM4 VU29P FPGA,可实现新一代网络平台。VCU129 评估套件展示了 Xilinx SerDes 技术的领先地位,可充分利用 Xilinx 无盖封装方法的低成本散热设计。VCU129 具有多种通用高速互连、板载内存和 PCIe®Gen 3 接口。

在项目中,CERN研究人员通过将AI推理和性能关键传感器的预处理在部署于大型强子对撞机(LHC)中的Xilinx Virtex Ultrascale FPGA上结合,通过自行设计的一套HLS4ML的软件工具,可定制计算极大的加速了处理能力, 并且使得神经网络推理的延时降低到100ns数量级

在赛灵思硅谷总部实验室抢鲜了解 Versal™。领略 Hello World、AI 引擎、片上网络(NoC)、PCIe、32G 收发器和搭载了多速率 MAC(MRMAC)的业界首款 ACAP,该 MAC 基于 7 nm 处理技术,现已向抢鲜体验客户发货

该系列前两篇主要扯了扯Linux中GUI相关的DRI框架及相关组件实现方式。细想一下,对于GUI相关的加速能做的其实不多,开发一个2D或3D的显卡加速子模块对于一个DEMO教程的量级来说工作量太大,我们在这只实现一下简单的功能

Falcon 计算基因组加速平台 (FGAP) 与 Xilinx 合作,既能够在支持 XBB 的本地电气设备上无缝工作,也能够在公共云上无缝工作。在云端,该平台目前在 AWS、华为以及阿里巴巴云的 FPGA 实例上提供。

Xilinx GEMX(通用矩阵运算)库可提供一套高性能引擎,用于加速严重依赖矩阵运算的应用。该库附带了一组能够支持软件的 Python API,特别是 Python 开发人员可以轻松利用这些引擎的性能优势。

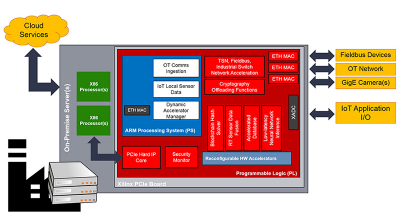

工业应用总是在及时寻找正确的答案。Xilinx SoC 及 FPGA 中的确定性、低时延计算与通信是在传统工业环境或智慧城市中融合 IT/OT 网关和雾计算的理想选择。无论端点处理如何混合以补充云计算、有线及无线通信协议的桥接,Xilinx 解决方案都将锚定在强大硬件可信性架构上,以实现稳健的网络安全性

如今的高端设备功耗和发热量越来越夸张,相应的散热设计也是越来越疯狂,日常的多风扇、水冷,极限超频的液氮、液氦等等无所不用其极。台北电脑展上,迪兰恒进展示了一种堪称终极的风冷散热设计。散热对象是一块赛灵思(Xilinx)的高端FPGA卡,集成两个100GbE十万兆网卡,可用于智能网卡(SmartNIC)、机器学习等