【视频】高密度计算服务器中的推断加速

judy 在 周四, 01/10/2019 - 15:02 提交

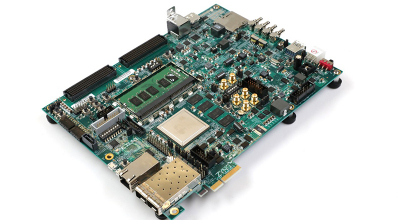

此演示展示了一个密集的 AMD EPYC 服务器,支持多达八个 Alveo U200 / U250 加速卡,可为计算密集型应用提供最高的自适应计算密度。该系统还配备了一款超微主板。该系统可用来加速基因组学、视频、大数据以及金融等领域的应用。

此演示展示了一个密集的 AMD EPYC 服务器,支持多达八个 Alveo U200 / U250 加速卡,可为计算密集型应用提供最高的自适应计算密度。该系统还配备了一款超微主板。该系统可用来加速基因组学、视频、大数据以及金融等领域的应用。

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用。或者直接生成比特流下载文件。能够加快DSP系统的开发进度。

一、Black Box调用HDL代码

1、简介

System Generator提供了一个特性:可以通过black box这个block将其它HDL文件以黑盒的形式封装到System Generator设计中,在仿真时使用Simulink+Vivado Simulator(或ModelSim)协同仿真的方法,在Simulink环境中完成设计的仿真测试。

具体介绍大家可以查阅相关资料。

2、本部分设计使用到的block

Xilinx block

其它block

该系列文章介绍MIPI系列规范。本篇为第一篇,主要介绍MIPI Alliance及其推出的一系列规范,以及相关的一些应用,以便对MIPI有一个全面的了解。后续会针对每一个部分进行详细介绍。

1、MIPI Overview

DDS直接数字式频率合成器(Direct Digital Synthesizer)。本文实现一个具有可以频率可调、相位可调的正余弦、方波、三角波的DDS。

使用 Vivado 设计套件中的各种设计分析特性。

内核重置应该保持断言状态,直到相关时钟稳定为止。在从重置中取出以太网 IP 核之前,它必须具有稳定的频率而且没有故障。 这适用于 SerDes 时钟和 IP 核时钟。 如果在一个时钟中检测到后续不稳定性,就必须重置 100G 以太网 IP 核。

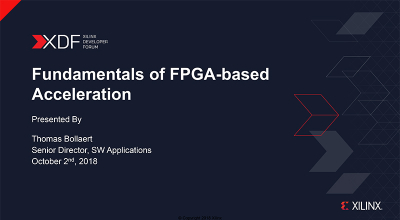

基于 FPGA 的加速原理

很多使用ZCU106/104开发板的小伙伴,发现在官网上可以找到包括IPI,MIG,PCIe等参考设计,但是如何把VCU用起来的流程设计,Target Reference Design(以下简称TRD)不知道哪里去下,那么最新版本的TRD去哪里获得呢?

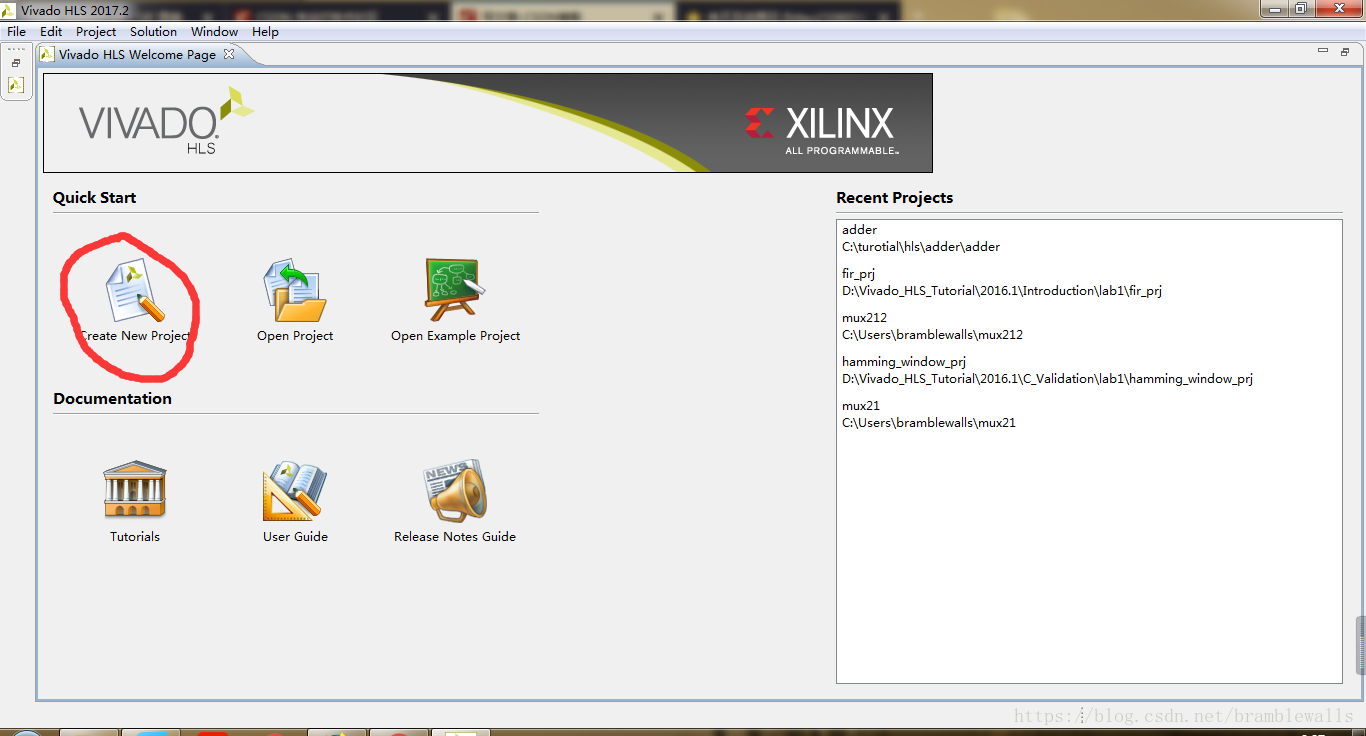

一、用HLS生成一个定制IP(加速器)

(1)首先打开vivado hls,本人的版本是2017.2,点击创建一个新工程。

(2)设置工程名和路径,顶层函数设置为add,创建一个新的C++程序,名字叫做adder.cpp,不用在testbench中添加文件。

选择板子的时候搜索xc7z020clg400-1,这是PYNQ的板子号,选择完成。

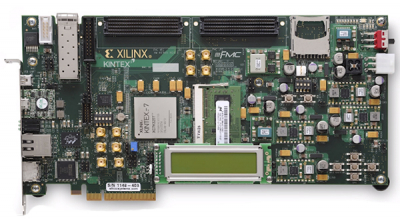

视频演示了 DDR3 内存的 Kintex-7 FPGA 接口功能。