基于 Xilinx 的大规模 MIMO 方案和 5G 小蜂窝基站部署

judy 在 周四, 07/18/2019 - 09:25 提交

RFDSP CEO(创意信息首席科学家)梁平院士将向大家介绍他们对于 O-RAN 的理解,以及他们所带来的诸多 5G 产品。包括 64T/64R 大规模 MIMO 平台,基于无线电前馈模块的 4D/4R 解决方案等等

RFDSP CEO(创意信息首席科学家)梁平院士将向大家介绍他们对于 O-RAN 的理解,以及他们所带来的诸多 5G 产品。包括 64T/64R 大规模 MIMO 平台,基于无线电前馈模块的 4D/4R 解决方案等等

图像处理简而言之就是对图像进行操作从而得到自己想要的结果,它是一个非常广义的概念,包含图像增强、图像复原、图像重建、图像分析、模式识别、计算机视觉等N多个应用方向。这些应用技术有许多在本质上是相通的,但是不同应用领域的关注点往往是不同的

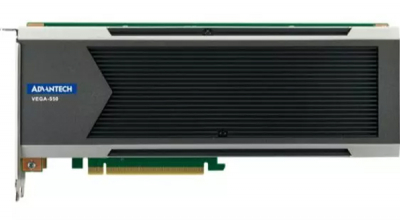

Advantech 在 AI 、IoT 智能系统与嵌入式平台领域居于全球领先地位。他们正在开发新系列的 IoT、大数据和人工智能软硬件产品。他们的边缘智能 WISE-PaaS 核采用赛灵思技术开发,是他们的产品核心。最近,Advantech 成功地将赛灵思 DPU 部署到其采用四个 ZU7EV 器件的定制板 VEGA-550 上

赛灵思为 AI 应用提供了全面的硬件和软件支持,关注赛灵思微信,每个月您都能收到我们在 AI 相关领域的最新动向和资料更新,从设计范例,IP和工具,实例演示,到 技术文档等内容的更新,不一而足,干货满满。

观看视频,了解传感器融合之王 SP701 评估套件可以实现哪些功能。

前几天聊天聊到在Linux系统下调用SDK的gnu交叉编译工具链的问题,Panda同学是这么做的,简单写几句分享一下。按照正常套路,我们会专门下载第三方交叉编译工具链进行Xilinx器件的Linux开发

Verilog语言和VHDL语言是两种不同的硬件描述语言,但并非所有人都同时精通两种语言,所以在某些时候,需要把Verilog代码转换为VHDL代码。本文以通用的XHDL工具为例对Verilog转换到VHDL过程中存在的问题进行了总结

SumUp Analytics 的 Nucleus 平台是一个提供 Xilinx FPGA 支持的实时文本分析 SaaS 算法,用于从非结构化文本中识别、提取和分析重要信息。该平台在采用 Alveo™ U200 加速器卡的本地设备或 AWS EC2 F1 实例上无缝工作。Nucleus 不仅包括一个运行在 Xilinx FPGA 上的 Python/SDAccel 混合库,用于核心分析,而且还包括用于外设分析的分布式 CPU

SP701 评估套件配备业界最佳性能功耗比 Spartan®-7 FPGA,适用于需要传感器融合的设计,如工业网络、嵌入式视觉和汽车等应用。SP701 通过 Pmods 和 FMC 连接器提供高 I/O 可用性和 I/O 扩展,使其成为 Spartan-7 FPGA 用户最大的 IP 开发平台。所包含的 XC7S100 FPGA 是 Spartan-7 系列中密度最大的器件。

使用 Xilinx 深度学习处理器(DPU)IP 构建自定义系统,使用面向 Xilinx SoC 的 DNNDK 优化经过训练的推断模型。