加速,为啥要用FPGA?——从软件到FPGA开发

judy 在 周一, 07/01/2019 - 09:39 提交

技术这个东西,如果只是用在工作岗位上的话,就是一个“搬砖”的工具,如果把它分享出来,没准还能碰撞出有意思的东西来,你们说是吧?好了,这一系列博文教程叫做“FPGA软硬件加速入门”,顾名思义,就是利用FPGA本身的特点,在软硬件进行不同的系统分工,加速系统输出的速度(主要是计算),我会尽量从入门者的角度讲解相关内容

技术这个东西,如果只是用在工作岗位上的话,就是一个“搬砖”的工具,如果把它分享出来,没准还能碰撞出有意思的东西来,你们说是吧?好了,这一系列博文教程叫做“FPGA软硬件加速入门”,顾名思义,就是利用FPGA本身的特点,在软硬件进行不同的系统分工,加速系统输出的速度(主要是计算),我会尽量从入门者的角度讲解相关内容

ESIstream是一个开源的串行数据接口协议,成本极低,支持多种FPGA架构的简单硬件实现,并占用最小的资源。简单来说,它是JEDEC的JESD204B子集1和2标准的开源替代方案。另外,ESIstream可为用户带来很多好处,这里将讨论其中的一些,包括低复杂度、低链接延迟和实现确定性延迟的简单方案。

2019年6月26-28日,2019 MWC(世界移动通信大会)在上海新国际博览中心展出。作为业界唯一提供灵活应变的 5G 通信平台的供应商,赛灵思应邀在 5G 网络论坛商做主题演讲。来自赛灵思公司的无线系统架构师,Matt Ruan(阮铭博士)与众多与会者共同分享赛灵思的自适应、智能化的 5G 趋势,以及赛灵思所提供的方案和技术

体验引人瞩目的 Versal™ AI 引擎的实际表现,您将看到一系列兼具软件可编程和硬件自适应的 1GHz+ VLIW、SIMD 矢量处理内核,它具有硬化的计算单元与紧密耦合的存储器。借助 Versal AI 引擎,我们将助力您实现突破性的 AI 推断和先进的信号处理加速

现场可编程门阵列(FPGA)是实现这些愿景的特定计算硬件之一。为了让我们的读者更好地了解这项技术,Yole软件和计算市场与技术分析师Yohann Tschudi博士采访了赛灵思(Xilinx)高级总监Willard Tu先生,与其交流了FPGA在未来自动驾驶中的关键作用

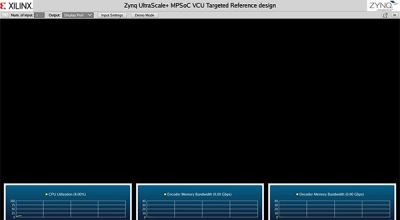

在VCU TRD 2019.1的Linux里,使用devemem读写内存,得到错误“devmem: mmap: Operation not permitted”。

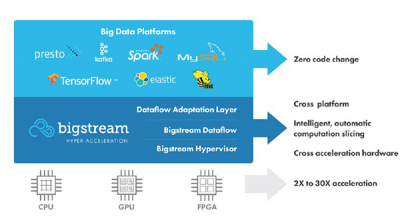

Bigstream Hyper 加速层可为大数据平台用户实现加速过程自动化。它由通过原生 C++ 实现的软件加速编译技术和 FPGA 加速模板组成。

在2019年,企业将利用工业制造领域的进步技术,并采取更大胆的措施来提高增长和运营效率。以下是2019年工业物联网的主要趋势和预测。

本视频介绍了 Versal 自适应的片上网络 (NOC)。 这种固有的软件可编程创新确保了该平台一经启动,即可供硬件设计师和软件开发者使用。 Versal 的各种引擎、关键接口和集成存储器控制器通过这条高效低耗的超高速连接和驱动,为定制型异构硬件解决方案带来高带宽和低时延

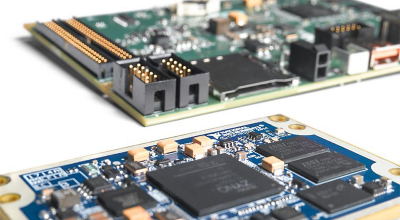

将直接射频采样数据转换器与Xilinx的小体积、低功耗逻辑相结合,为开发各种高性能射频设计提供了理想的平台。