AMD Versal系列FPGA NoC介绍及实战

judy 在 周五, 07/14/2023 - 10:55 提交

NoC是相对于SoC的新一代片上互连技术,从计算机发展的历史可以看到NoC 必将是SoC 之后的下一代主流技术

NoC是相对于SoC的新一代片上互连技术,从计算机发展的历史可以看到NoC 必将是SoC 之后的下一代主流技术

依托 AMD 自适应计算技术,Xnext 开发出了一种名为 XSpectra 的革命性食品检测技术

AMD的技术广泛应用在金融、电信、制造、教育和医疗等各行各业

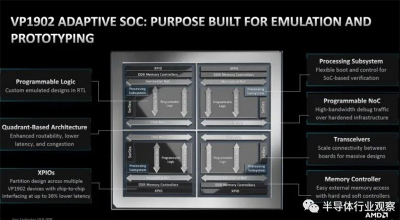

在设计规模和复杂性不断增长的世界里,SoC 和 FPGA 设计需要以更低功耗提供更高性能

本文展示了在AMD Zynq设计中,如何用 Vitis Vision Library中的函数导出一个 IP

Vitis高层次综合可通过在选定的 AMD 器件上将 C/C++ 代码综合为可编程逻辑的 RTL 代码

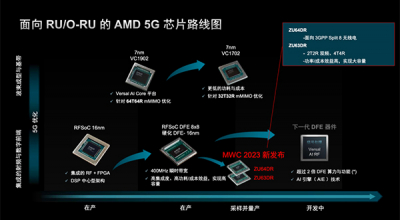

展示了基于领先的 AMD FPGA、自适应 SoC 以及 AMD EPYC™ 处理器的通信领域解决方案

通信业已经进入5G时代。运营商投资建网、设备商提供各类5G设备和解决方案

新型 AMD Versal Premium VP1902 有效地将可模拟多达 1850 万个逻辑单元的门数增加了一倍

第三代AMD EPYC处理器采用7nm工艺,可以提供至高64个计算核心