【分享】在PL设计中使用MPSoC EMIO GPIO,并使用脚本设置MPSoC EMIO GPIO

judy 在 周四, 08/06/2020 - 11:15 提交

MPSoC 为PL提供了96个GPIO,通过EMIO管脚链接到PL。普通PL设计,一般只会用到几个GPIO管脚。可以使用Vivado IPI中的Slice IP, 从其中分出指定数量的管脚。

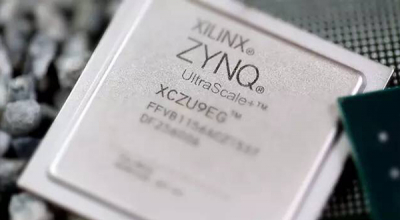

Zynq® UltraScale+™ MPSoC(多处理器系统芯片)是赛灵思(Xilinx)推出的一款集成了处理器系统和可编程逻辑的器件。这一系列芯片采用 UltraScale+ 架构,结合 ARM 处理器和可编程逻辑,为嵌入式系统提供了灵活性和高性能。

Zynq UltraScale+ MPSoC 适用于嵌入式系统设计,特别是对于需要高度定制和硬件加速的应用。它为设计人员提供了处理器和 FPGA 的集成解决方案,以满足各种复杂系统的需求。

MPSoC 为PL提供了96个GPIO,通过EMIO管脚链接到PL。普通PL设计,一般只会用到几个GPIO管脚。可以使用Vivado IPI中的Slice IP, 从其中分出指定数量的管脚。

赛灵思今天宣布,搭载赛灵思车规级芯片平台 Zynq® UltraScale+™ MPSoC 的百度 Apollo 自动驾驶计算平台 ACU 于伟创力中国苏州工厂正式量产下线,这款量产的 ACU 硬件平台将率先应用于 Apollo Valet Parking( AVP )自主泊车产品。

米尔科技的FZ3是与百度紧密合作推出的一款基于Xilinx Zynq Ultrascale CZU3EG芯片打造的深度学习计算卡,芯片内部集成了4核ARM A53处理器+GPU+FPGA的架构,具有多核心处理能力、FPGA可编程能能力以及视频流硬件解码能力等特点。

不同使用场景,对芯片的性能和功耗要求不一样。为了测试Xilinx MPSoC PS侧的最低功耗,基于ZCU106单板做了功耗优化。为了方便,使用最简单的软硬件环境。软件使用死循环做串口打印,硬件保留了如下模块。

本文介绍MPSoC的芯片启动流程

本文展示了通过使用 Design Gateway 的 NVMeG3-IP 内核在 Xilinx 的 ZCU102 评估套件上实现 NVMe 固态硬盘 (SSD) 接口的解决方案,该方案可实现惊人的快速性能:写入速度达 2,319 MB/s,读取速度达 3,347 MB/s。

本文演示了使用Vivado设计套件和Xilinx软件开发套件构建基于Zynq UltraScale + MPSoC处理器的嵌入式设计。提供有效的嵌入式系统设计的动手教程。

有些应用中,需要降低Xilinx MPSoC的功耗。缺省设置中,R5/GPU都被使能。如果需要省电,可以在Vivado里关闭R5/GPU。步骤如下:

1. 选中 MPSoC IP,在右键菜单中选择Block Properties.

2. 在窗口Block Properties中,选择Properties.

得益于人工智能的发展,它在机器人、物联网和智能个人助理(如Siri和Alexa)等方面创造了惊人的发展。那什么是人工智能呢?人工智能最简单的定义是:收集有关世界的数据,并利用这些数据进行短期和长期的预测。

Zynq UltraScale+ MPSoC 启动时间估算器电子表显示,QSPI 的闪存频率为 13.89MHz。如何达到该频率?