Xilinx、Spline.AI、AWS 推出 X 射线分型深度学习模型和参考设计

judy 在 周三, 11/18/2020 - 10:02 提交

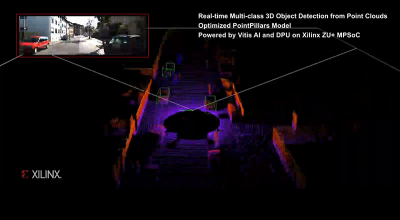

赛灵思宣布推出全功能医疗 X 射线分型深度学习模型和参考设计套件,这是赛灵思与 Spline.AI 及亚马逊网络服务(AWS)强强携手共同取得的合作成果。这种高性能模型部署在赛灵思 Zynq® UltraScale+™ MPSoC ZCU104 器件之上,并采用了赛灵思深度学习处理器单元(DPU)。该 DPU 是一种软 IP 张量加速器,它的强大功能足以支持运行各种神经网络