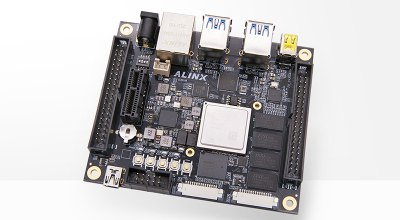

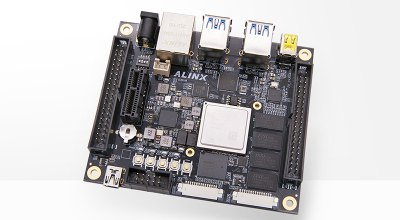

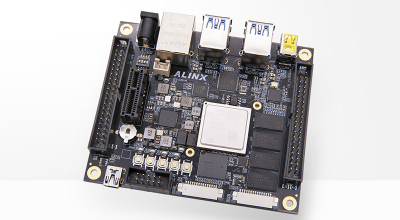

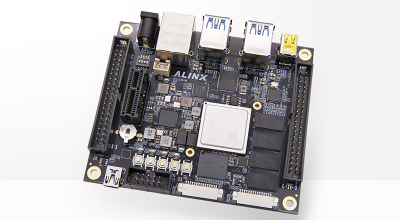

【ZYNQ Ultrascale+ MPSOC FPGA教程】第九章Vivado下按键实验

judy 在 周一, 01/04/2021 - 10:13 提交

按键是FPGA设计当中最常用也是最简单的外设,本章通过按键检测实验,检测开发板的按键功能是否正常,并了解硬件描述语言和FPGA的具体关系,学习Vivado RTL ANALYSIS的使用。

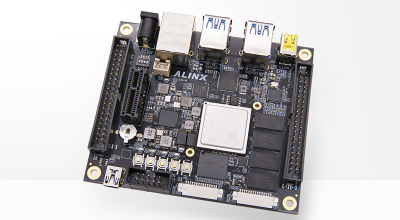

Zynq® UltraScale+™ MPSoC(多处理器系统芯片)是赛灵思(Xilinx)推出的一款集成了处理器系统和可编程逻辑的器件。这一系列芯片采用 UltraScale+ 架构,结合 ARM 处理器和可编程逻辑,为嵌入式系统提供了灵活性和高性能。

Zynq UltraScale+ MPSoC 适用于嵌入式系统设计,特别是对于需要高度定制和硬件加速的应用。它为设计人员提供了处理器和 FPGA 的集成解决方案,以满足各种复杂系统的需求。

按键是FPGA设计当中最常用也是最简单的外设,本章通过按键检测实验,检测开发板的按键功能是否正常,并了解硬件描述语言和FPGA的具体关系,学习Vivado RTL ANALYSIS的使用。

FIFO是FPGA应用当中非常重要的模块,广泛用于数据的缓存,跨时钟域数据处理等。学好FIFO是FPGA的关键,灵活运用好FIFO是一个FPGA工程师必备的技能。本章主要介绍利用XILINX提供的FIFO IP进行读写测试。

FPGA本身是SRAM架构的,断电之后,程序就消失,那么如何利用FPGA实现一个ROM呢,我们可以利用FPGA内部的RAM资源实现ROM,但不是真正意义上的ROM,而是每次上电都会把初始化的值先写入RAM。本实验将为大家介绍如何使用FPGA内部的ROM以及程序对该ROM的数据读操作。

自动驾驶发展至今,在更加严格的安全等级和功耗成本限制下,实现高级自动驾驶,对充当自动驾驶“大脑”的域控制器提出了更高的要求。除了特斯拉等业界巨头,能够在这个领域落地的方案可谓凤毛麟角。而成立于 2018 年的宏景智驾,便是这个高级自动驾驶赛道的领先探险者之一。

在基于供电网络 (PDN) 的共振峰创建的布局前、布局后和系统验证数据模式中分析电源完整性对 FPGA DDR4 存储器接口中的信号完整性的影响。使用 FPGA 配置的矢量网络分析仪 (VNA) 测量 PDN 阻抗曲线。创建多个测试数据模式,以便将电源的电流频谱分量与 PDN 共振峰叠加在一起,并演练传输线多次反射累积效应

Zynq UltraScale+ MPSoC VCU DDR 控制器是一款专用 DDR 控制器,只支持在 Zynq UltraScale+ MPSoC EV 部件上与 Zynq UltraScale+ MPSoC VCU(H.264/H.265 视频编解码器)连用。

因此,调试将不同于 MIG 等传统 Xilinx DDR 控制器。

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。

使用 2018.2 Ultra96 PetaLinux BSP 构建图像时,如果我在 Matchbox 桌面点击关断图标,电路板不关断。服务器窗口会关闭,屏幕变为空白,但电路板还在运行。

在本例程中,我们要做的是LED灯控制实验,每秒钟控制开发板上的LED灯翻转一次,实现亮、灭、亮、灭的控制。会控制LED灯,其它外设也慢慢就会了。

NeoPixels是数字控制的红、绿、蓝像素。由于每种颜色都由8位表示,总共24位,因此每个像素可以显示16777216种颜色中的一种。每个NeoPixel实际上是一个WS2812 LED。这些LED包含五个输入端,相对于地(VSS)在3.3V到5.0V(VDD和VCC)的电压范围内工作。