【工程师分享】升级Vivado工程脚本

judy 在 周五, 06/04/2021 - 11:46 提交

Vivado可以导出脚本,保存创建工程的相关命令和配置,并可以在需要的时候使用脚本重建Vivado工程。脚本通常只有KB级别大小,远远小于工程打包文件的大小,因此便于备份和版本管理。下面把前述脚本升级到Vivado 2020.2为例,讨论如何升级Vivado工程脚本。

Vivado是赛灵思(Xilinx)公司推出的一款集成开发环境(IDE),用于设计和开发基于FPGA(可编程逻辑器件)的数字电路。Vivado提供了一个全面的工具套件,支持从设计到验证、实现和编程的全过程。

Vivado是一种全面的FPGA设计工具,适用于各种应用,包括通信、图像处理、数字信号处理、网络加速和嵌入式系统设计。

Vivado可以导出脚本,保存创建工程的相关命令和配置,并可以在需要的时候使用脚本重建Vivado工程。脚本通常只有KB级别大小,远远小于工程打包文件的大小,因此便于备份和版本管理。下面把前述脚本升级到Vivado 2020.2为例,讨论如何升级Vivado工程脚本。

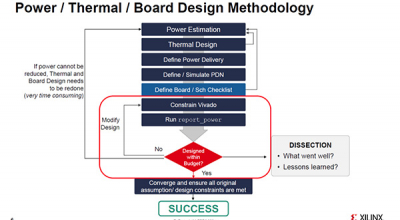

本视频讨论功耗约束以及报告功耗估算的最佳实践。

本视频将讲解提高结果质量的最新方法窍门与技巧。

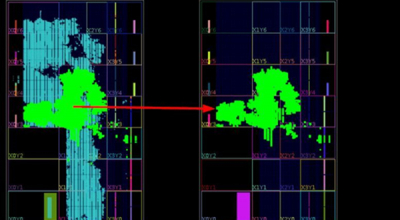

本文旨在提供一种方法,以帮助设计师判断给定模块是否能够在空裸片上达成时序收敛。 如果目标模块无法在空裸片上达成非关联 (OOC) 时序收敛,则恐难以与设计其余部分达成关联性时序收敛。设计师可从完整设计中提取目标模块、对其进行布局规划、约束,然后通过实现工具来运行这些模块,以判断是否能够独立达成时序收敛。

本视频重点讨论动态功能交换Dynamic Function eXchange

本视频将探讨Vivado IP集成器的特效与优势以及它如何帮助您解决复杂的设计问题。

本文详细介绍Vivado工具对FPGA设计进行逻辑和时序分析的特点,以及工具生成的报告和信息。讨论实现时序收敛的方法,包括审查时钟树和时序约束,设计底层规划,以及平衡运行时间和结果。

本文描述了Vivado仿真器作为独立工具和Vivado设计套件的一部分的使用,以及使用波形查看器来分析和调试设计。记录RTL设计的行为仿真,以及综合和实现设计的功能和时序仿真。

4月23日,Xilinx Adapt China:Vivado专场的第二天,赛灵思 Vivado专家团将带来连续三场的“设计收敛”技巧分享。从如何提高QoR(结果质量)的方法技巧、解决接受的时序问题工具,到功耗约束的最佳实践,诚意满满,技术干货一应俱全。

本文介绍 Vivado® 集成设计环境 (IDE),它提供了直观的图形用户界面 (GUI),用于可视化和与 FPGA 设计交互。描述了Vivado IDE如何帮助您配置工具选项、分析和完善时序,以及设计平面图以改进结果。