vivado2021.1添加w25q128型号flash的方法

judy 在 周三, 03/29/2023 - 09:24 提交

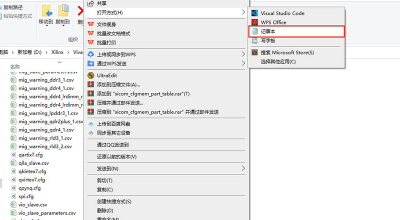

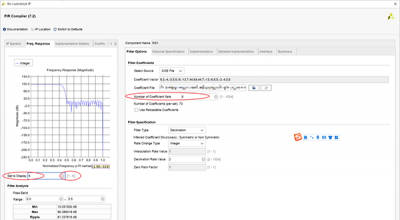

找到[安装目录]\2021.1\data\xicom下的xicom_cfgmem_part_table.csv文件

Vivado是赛灵思(Xilinx)公司推出的一款集成开发环境(IDE),用于设计和开发基于FPGA(可编程逻辑器件)的数字电路。Vivado提供了一个全面的工具套件,支持从设计到验证、实现和编程的全过程。

Vivado是一种全面的FPGA设计工具,适用于各种应用,包括通信、图像处理、数字信号处理、网络加速和嵌入式系统设计。

找到[安装目录]\2021.1\data\xicom下的xicom_cfgmem_part_table.csv文件

本文提供了仿真进程以及 Vivado® Design Suite 中的仿真选项的概述

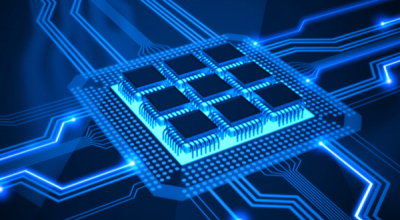

在信道化到处理中有可能会涉及到滤波器变带宽的需求,这时可以利用IP(以Xilinx为例)提供多系数组功能

RS码是一种常用的纠错编码,本文主要介绍如何在vivado环境下利用RS IP核实现RS码的编译码。

在调试时序约束的过程中,用户常常会对除了顶层约束外所涉及的繁杂的时序约束感到困惑而无从下手。

Ubuntu20.04LTS中使用Vivado 2021.2时,每次重启Vivado,文本编辑界面的字体大小就会变成默认大小。

为了推断UltraRAM,你需要在所需的内部阵列上使用一个资源指令。

Vivado支持工程模式(ProjectBased Mode)和非工程模式(NoneProject Mode)两种,且都能通过Tcl脚本批处理运行。目前,更多的人使用的是工程模式,今天我们就基于工程模式介绍几个Tcl命令的使用方法。

我已将我的设计迁移到更新版本的 Vivado 工具。当我在 SDK 中调试时,调试器显示的是汇编代码,而不是 C 或 C++。为什么会出现这种情况?

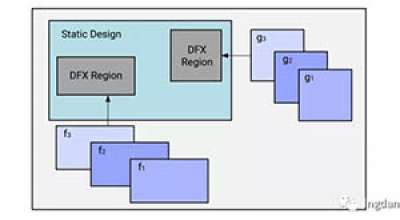

使用 DFX 有助于设计者转而采用更少或更小的器件,降低功耗并提高系统升级能力。随时按需加载功能,更有效利用芯片。