AXI总线详解-不同类型的DMA

judy 在 周三, 09/23/2020 - 09:33 提交

几个常用的 AXI 接口 IP 的功能(上面已经提到):

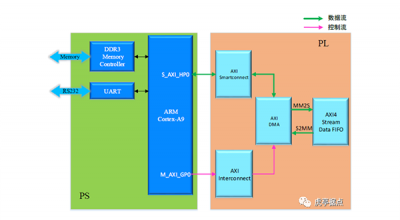

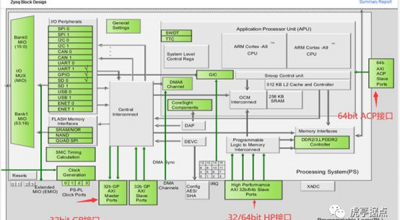

AXI-DMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换

AXI-FIFO-MM2S:实现从 PS 内存到 PL 通用传输通道 AXI-GP<----->AXI-Stream 的转换

几个常用的 AXI 接口 IP 的功能(上面已经提到):

AXI-DMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换

AXI-FIFO-MM2S:实现从 PS 内存到 PL 通用传输通道 AXI-GP<----->AXI-Stream 的转换

在上一篇中着重讲解了DMA的含义和AXI_DMA_IP,本次的重点就是搭建一个AXI_DMA环路工程,并从C语言角度分析其SDK代码

DMA是一种内存访问技术,允许某些计算机内部的硬件子系统可以独立的直接读写内存,而不需要CPU介入处理,从而不需要CPU的大量中断负载,否则,CPU需要从来源把每一片段的数据复制到寄存器,然后在把他们再次写回到新的地方,在这个时间里,CPU就无法执行其他的任务

DMA外设特点:

DMA引擎拥有一个灵活的指令设置DMA的传输;

拥有8个cache线,每一个cache线宽度是4个字;

拥有8个可以并行的DMA通道线程;

拥有8个中断给中断控制器;

拥有8个DMA触发事件并且可以编码控制;

128个(64bit)的MFIFO,在传输的时候读写端可写入到此FIFO;

支持任意内存到内存的传输;