构建BittWare的数据包解析器,HLS与P4的实现对比

judy 在 周五, 08/27/2021 - 10:26 提交

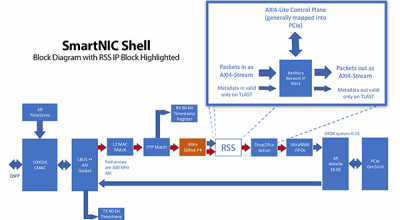

BittWare的SmartNIC Shell和BittWare的Loopback Example的功能之一是一个数据包解析器/分类器,它可以从数据包中提取协议字段。通过这篇白皮书,我们不仅要描述我们的Parser,还要解释如何使用HLS来构建和配置它,从而获得比使用P4语言更好的实现。

BittWare的SmartNIC Shell和BittWare的Loopback Example的功能之一是一个数据包解析器/分类器,它可以从数据包中提取协议字段。通过这篇白皮书,我们不仅要描述我们的Parser,还要解释如何使用HLS来构建和配置它,从而获得比使用P4语言更好的实现。

大多数FPGA程序员认为,高级工具总是发出更大的比特流,作为提高生产率的"成本"。 但事实总是如此吗?在本文中,我们展示了一个真实的例子

在本文中,我们将重点放在如何能够在不需要特殊的库或类的情况下修改代码风格以实现C代码实现并行性。Xilinx HLS 编译器的显着特征是能够将任务级别的并行性和流水线与可寻址的存储器 PIPO或 FIFO相结合。

高层次综合(High-level Synthesis)简称 HLS,指的是使用C、C++、System C 等高层次语言描述电路设计的逻辑结构,以及编写对应的测试激励,借助高层次综合工具,配合高阶约束文件及优化指令自动转换成低抽象级语言(VHDL/Verilog)描述的电路模型的过程。

了解 Xilinx HLS 技术如何使用可移植的 C 代码提取和实现任务并行。

本视频基于 developer.xilinx.com 上推出的文章

经常听人说,Verilog或VHDL与HLS相比,就好比是几十年前的汇编语言与C语言,HDL迟早会被HLS取代的。这些话已经讲了有一二十年了,还是没有看到HLS取代HDL。本文翻译自2019年TCAD杂志上一篇综述,调研和对比了近年已发表论文中采用HLS和HDL的各种使用情况,值得一看。

Vitis视觉库可用于构建Vivado®HLS中的应用程序。本节详细介绍如何将Vitis vision库组件集成到Vivado HLS 2019.2的设计中。本节提供了有关如何通过Vivado HLS 2019.2 use flow运行单个库组件的步骤,其中包括C仿真、C合成、C/RTL联合仿真以及将RTL作为IP导出

自定义 RTL Verilog 代码可以替换 HLS 项目中的 C 函数。 然后,通过 JSON 文件并使用 ap_ctrl_chain 协议将 RTL 编织到其余 C 代码中,以管理 RTL 和 C 代码之间的数据事务。

XTP系统拥有“极速交易、极速行情、极致风控、极致体验”等核心性能及优势,赛灵思是自适应计算技术与方案的领导企业。在本届开发者大会上,中泰证券将与赛灵思公司强强联手,带您体验 FPGA 为 Fintech 应用所带来的极速体验。

FPGA在fintech领域的应用历史悠久,Virtex时代就可见高频交易的应用。FPGA由于其内部逻辑及计算单元的丰富性和灵活性,可定制低延时、高吞吐率的设计,基本上可以碾压软件实现的性能。