基于HLS的视频缩放测试

judy 在 周三, 07/31/2019 - 09:14 提交

下面向大家介绍了使用HLS封装的缩放IP来实现视频图像缩放功能。将HLS封装的缩放IP加入到OV5640图像传输系统,验证图像放大和缩小功能。

下面向大家介绍了使用HLS封装的缩放IP来实现视频图像缩放功能。将HLS封装的缩放IP加入到OV5640图像传输系统,验证图像放大和缩小功能。

你想加速您的系统开发流程吗?你渴望借助“硬件加速”来提升系统性能吗?你希望用 C/C++ 抽象语言来编程 SoC 吗?赛灵思 SDSoC 开发环境可以帮你实现上述所有愿望。该软件开发环境将让你可以用 C/C++ 直接开发和优化基于 Zynq SoC 和 Zynq UltraScale+ MPSoC 软硬件系统,可实现系统级的特性描述、可编程逻辑中的自动软件加速

描述了用于提高设计吞吐量的 HLS PIPELINE 指令

介绍 Vivado® HLS 工具从 C 语言设计中抽象出来的端口级 AXI 接口协议。

了解由阵列引起的性能限制,并学习一些优化技术来处理阵列以提升性能

HLS高阶综合(high level synthesis)在被广泛使用之前,作为商业技术其实已经存在了20多年。设计团队对于这项技术可以说呈现出两极化的态度:要么坚信它是先进技术之翘楚,要么对其持谨慎怀疑态度。高级语言IP的优势是显而易见的,例如易维护性、在设计周期早期进行重大变更的能力、以及大大节省产品上市时间等方面的优势都很明显

背景:zynqNet运用HLS来实现相应的IPcore。相关HLS过程的信息会打印到console之中。目的:读懂HLS对IPcore代码的HLS过程,具体硬件如何实现。将报告信息存下来用于参考。

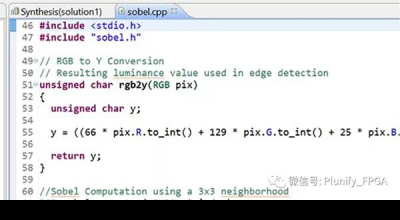

本文档重点探讨vivado HLS软件的使用,描述如何将相应的c程序用HLS转换为硬件可以实现的IPcore。

在HLS中使用帧间差分法生成了IP核,这里讲述如何在vivado中调用IP core

用软件从 C 转化来的 RTL 代码其实并不好理解。今天我们就来谈谈,如何在不改变 RTL 代码的情况下,提升设计性能。本项目所需应用与工具:赛灵思HLS、Plunify Cloud 以及 InTime。