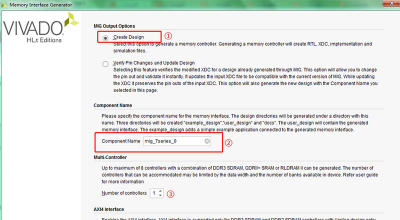

快速上手Xilinx DDR3 IP核(1)——MIG IP核的介绍及配置(Native接口)

judy 在 周二, 02/22/2022 - 09:56 提交

DDR3 SDRAM 简称 DDR3,是当今较为常见的一种储存器,在计算机及嵌入式产品中得到广泛应用, 特别是应用在涉及到大量数据交互的场合

DDR3 SDRAM 简称 DDR3,是当今较为常见的一种储存器,在计算机及嵌入式产品中得到广泛应用, 特别是应用在涉及到大量数据交互的场合

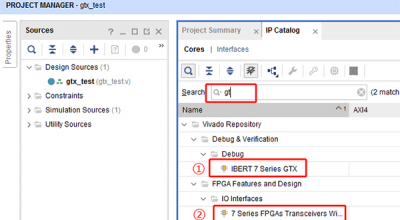

作为一名初学者,也曾被GTX一堆信号搞得头晕脑胀,在学习了各位大佬的文章后,结合自己的理解和实践,整理这一系列快速上手的GTX使用教程。

模块复用是逻辑设计人员必须掌握的一个基本功,通过将成熟模块打包成IP核,可实现重复利用,避免重复造轮子,大幅提高我们的开发效率。

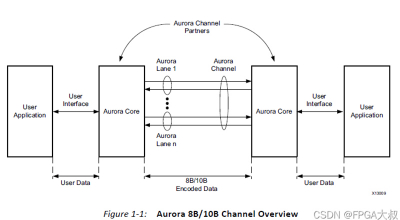

Aurora 广泛用于需要背板、电路板间和芯片间连接的应用。细分市场包括有线通信、存储、服务器、测试测量、工业、消费和医疗等。此外,Aurora 也可用作嵌入式处理器应用中的调试端口。

干货来了,用DDR搬砖,只需要会用IP就好,Xilinx官方YYDS!

以太网 IP 核的 1588 功能是用来实现,在 IP 内部为TX侧发送包打上发送出去这个时间节点的时间戳,以及获得 RX 侧收回来的包在 IP 接口处的时间戳。然而10G/25G 的 IP 例子工程没有提供演示,本文主要介绍了如何使用这个 IP 的 1588功能。

vivado提供了DDS IP核可以输出正余弦波形,配置方法如下

vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。今天介绍的是Vivado的三种常用IP核

vivado建立的工程经常会出现版本升级而导致的IP核锁定情况,本文以vivado 2019.2的版本打开旧版本为例,介绍两种更新方法

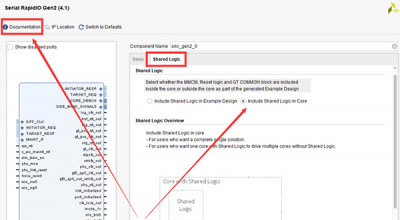

这里以Xilinx为例,在Vivado中使用SRIO高速串行协议的IP演示如何使用官方例程和手册进行快速使用,在仔细阅读参考官方例程后进行一些修改就可以应用在实际项目中。