手撕IP核系列——Xilinx FIR IP核之一

judy 在 周三, 08/24/2022 - 11:04 提交

在Xilinx和Intel平台的FPGA中提供了给我们各种各样的IP核,这些IP核都是厂家的成熟设计,使用起来也非常的方便

在Xilinx和Intel平台的FPGA中提供了给我们各种各样的IP核,这些IP核都是厂家的成熟设计,使用起来也非常的方便

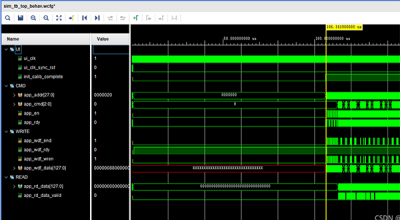

MIG IP控制器是Xilinx为用户提供的一个用于DDR控制的IP核,方便用户在即使不了解DDR的控制

一片RAM中分为许多小格,每一片容量为36k,根据设定的位宽决定了这片RAM可以存放分为几格

本实验要完成利用vivado中的DDS IP核对两个正弦波进行混频,实现数字下变频或者上变频。

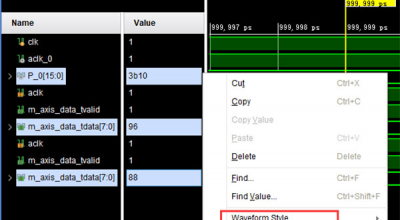

本文对xilinx FIFO IP的参数做详细解读

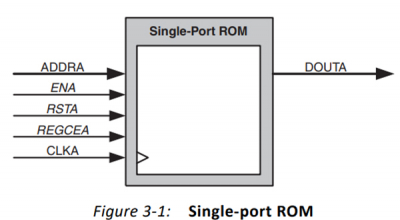

本文介绍一种在FPGA开发中非常常用的存储类 IP 核——ROM 的使用方法。

本文将对RAM IP核的各个关键因素做详细的讲解。

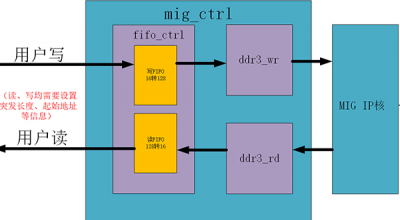

本文将把Xilinx的MIG IP核DDR3的Native接口进行二次封装,将其封装成一个类似FIFO的接口,使其应用起来更加方便简单。

本文将把Xilinx的MIG IP核DDR3的Native接口进行二次封装,将其封装成一个类似FIFO的接口,使其应用起来更加方便简单。

在我心中,Xilinx是一家完美的公司,技术生态支持实在是做的太好了。Xilinx也知道我们不会用DDR3,所以提供了一个example design给你学习,怎么样?惊不惊喜?意不意外?