多Aurora IP核的设计开发

francis zhang 在 周四, 04/06/2023 - 09:13 提交

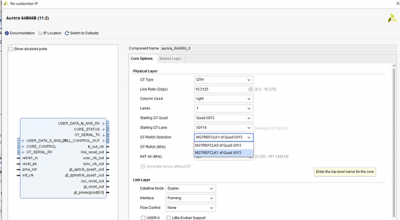

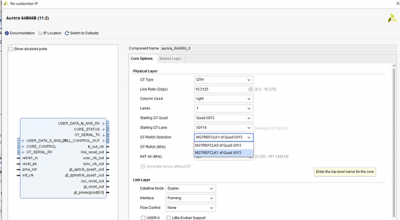

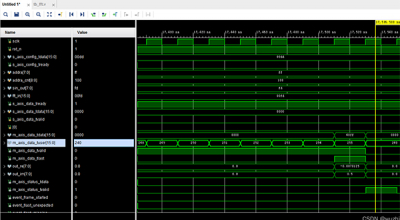

本文重点说明一下同一工程下多Aurora IP核如何配置使用

本文将Xilinx FFT IP核的使用方法及注意事项总结如下

在用vivado 生成IP核时,有两种综合方式:Global和out of context per IP。

通过阅读IP手册可以知道,该IP支持的很多种浮点数计算,今天主要介绍最简单的加法操作

本工程实现PCIE的8通道速率2.2GBps通信,并验证数据的正确性

学会如何根据手册配置 MIG IP 核中的参数。

从本文开始,我们详细介绍Xilinx CIC IP核滤波器相关知识,包括CIC IP核提供的特性

我们在利用FFT IP核进行FPGA设计时,需要理解FFT相关的操作理论,比如FFT蝶形运算带来的位宽扩展

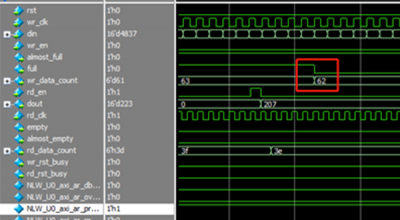

以前从来没有这么细扣过,认识比较肤浅,通过几天对Xilinx IP核的仿制,对异步FIFO有了更深刻的认识。

Xilinx LogiCORE IP快速傅立叶变换核实现了Cooley-Tukey-FFT算法,这是计算离散傅立叶变换(DFT)的有效方法