1分钟快速掌握 Vivado DDS IP核

judy 在 周二, 09/24/2024 - 10:25 提交

今天介绍一下非常好用的 Vivado DDS IP 核。

今天介绍一下非常好用的 Vivado DDS IP 核。

很多初学者刚开始看到PCIe IP文档时,不太懂Xilinx PCIe IP核主要的数据接口:CC、CQ、RQ、RC。本文主要就是对这些接口做详细的介绍,希望能答疑解惑。

RapidIO 互连架构旨在与最流行的集成通信处理器、主机处理器和网络数字信号处理器兼容,是一种高性能、分组交换互连技术

本文将从基础概念入手,逐步深入到AXI DataMover IP的配置和使用,帮助读者快速掌握这一强大的IP核。

DDR4 SDRAM因其高速、大容量的特点,在FPGA设计中扮演着越来越重要的角色。本文将详细介绍DDR4 MIG IP核及其配置过程。

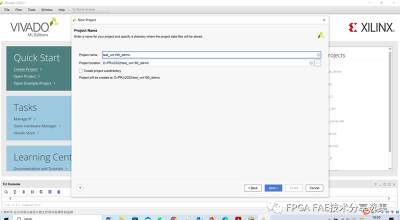

今天给大侠带来Vivado调用IP核详细操作步骤,手把手教学,请往下看

Vivado软件作为Xilinx FPGA器件重要的开发设计软件

本文来进一步讲解如何来建立CIPS IP核示例工程。

本文对CIPS主要功能模块做解析

本文主要介绍FIFO的一些基础知识,帮助大家能够理解FIFO的基础概念