JESD204B的应用场景

judy 在 周一, 12/12/2022 - 09:28 提交

接触过FPGA高速数据采集设计的朋友,应该会听过新术语“JESD204B”

接触过FPGA高速数据采集设计的朋友,应该会听过新术语“JESD204B”

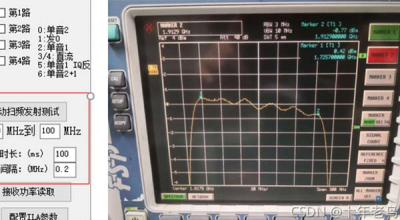

多掌握的技能总是会派上用场的时候,这里我又要用VB.net来方便自己的调试。

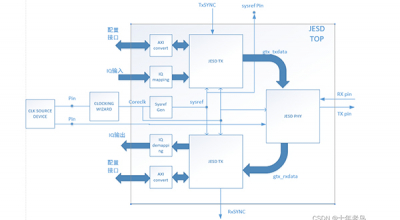

作为一个ADC和DAC接口,我们需要构建一个顶层模块

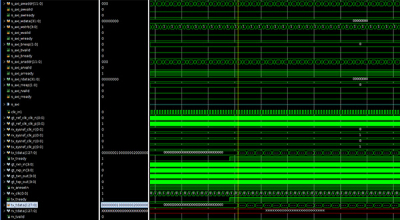

Xilinx JESD204B IP testbench解析

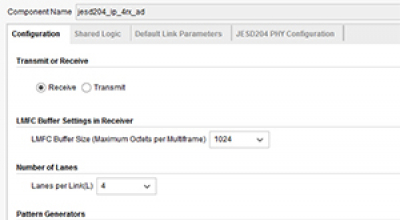

一般来说,如果在IPcore配置正确的话,不太需要通过AXI指令来进行参数的修改,不过如果能够支持AXI指令

JESD204B 标准中定义的确定性延迟机制要求多帧大小大于链路上的最大可能延迟。

进行工程的功能调试时,对AD9144,AD9516进行参数配置是非常重要且必不可少的,这过程中遇到了以下问题。

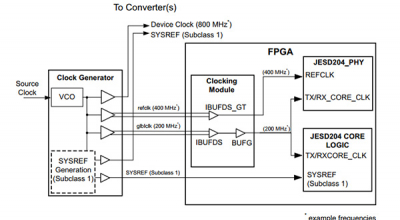

下面的图是JESD204B的时钟关系图,该图非常的重要,一般JESD204B同步不上,或者有其他错误的时候,就要重点检查时钟

系统主要采用官方JESD_PHY(免费),JESD_RX(评估版),JESD_TX(评估版)三个IP核做测试,采用自发自收,外部GT引脚回环方式。其中,PHY采用4个LANE接收和发送数据,一般线速率为参考时钟的40倍

为满足低电压数字讯号(LVDS)和并行输出ADC的需要,延迟不一致的问题,对系统设计人员而言是一个难题