ADC/FPGA串连顺畅 JESD204B界面故障排除无碍

judy 在 周四, 08/19/2021 - 11:31 提交

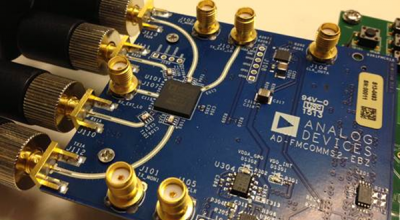

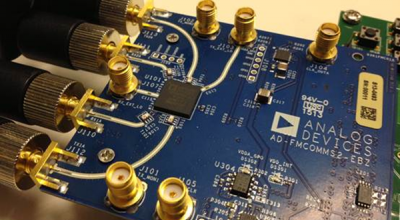

本文阐释了JESD204B标准的ADC与FPGA的接口,如何判断其是否正常工作,以及可能更重要的是,如何在有问题时排除故障。文中讨论的故障排除技术可以采用常用的测试与测量设备,包括示波器和逻辑分析仪,以及Xilinx的ChipScope或Altera的SignalTap等软件工具。同时说明了接口讯号传输,以便能够利用一种或多种方法实现讯号传输的可视化。

本文阐释了JESD204B标准的ADC与FPGA的接口,如何判断其是否正常工作,以及可能更重要的是,如何在有问题时排除故障。文中讨论的故障排除技术可以采用常用的测试与测量设备,包括示波器和逻辑分析仪,以及Xilinx的ChipScope或Altera的SignalTap等软件工具。同时说明了接口讯号传输,以便能够利用一种或多种方法实现讯号传输的可视化。

实现确定性延迟是当今许多系统设计中讨论的主题。过去,人们一直在努力提高数据传输速度和带宽。如今的应用则越来越重视确定性——即要求数据包在精确的、可重复的时间点传送。本文将在设备的层面讨论确定性这一主题,以及如何设计超高速数据转换和信号处理系统以保证确定性延迟。

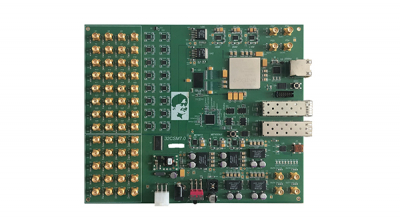

无论是设计测试和测量设备还是汽车激光雷达模拟前端(AFE),使用现代高速数据转换器的硬件设计人员都面临高频输入、输出、时钟速率和数字接口的严峻挑战。问题可能包括与您的现场可编程门阵列(FPGA)相连、确信您的首个设计通道将起作用或确定在构建系统之前如何对系统进行最佳建模。

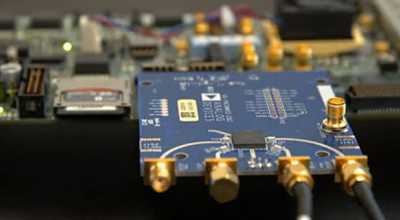

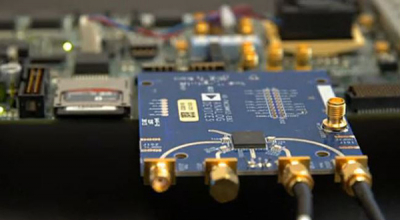

本篇的内容基于jesd204b接口的ADC和FPGA的硬件板卡,通过调用jesd204b ip核来一步步在FPGA内部实现高速ADC数据采集,jesd204b协议和xilinx 的jesd204 IP核相关基本知识已在前面多篇文章中详细介绍,这里不再叙述~

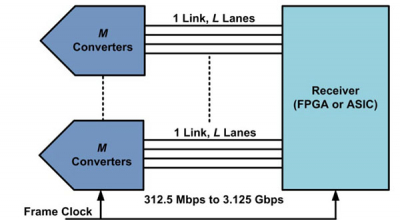

JESD204B是JEDEC委员会制定的一种串行接口标准,这种接口标准定义了数据转换器(ADC、DAC)和数字处理器(FPGA、 ASIC等)之间的数字信号传输方式。它作为第三代标准,补充了JESD204、JESD204A这前两代标准的不足之处。

ADC芯片会包含许多性能参数,而我们在选择ADC芯片时,其中有一项关键性的参数值得关注,即数字化的数据输出接口类型(the type of digital data output)。目前在高速ADC芯片中,使用最广泛的数据输出接口类型有3种

2006年4月,JESD204标准的最原始版本诞生,该标准描述了数据转换器(ADC或DAC)和接收器(FPGA或者ASIC)之间的吉比特串行数据传输链路(link)。在这个原始标准中,一个或多个数据转换器与接收器之间的串行链路被定义为有且只有一条数据通道(lane)

ESIstream是一个开源的串行数据接口协议,成本极低,支持多种FPGA架构的简单硬件实现,并占用最小的资源。简单来说,它是JEDEC的JESD204B子集1和2标准的开源替代方案。另外,ESIstream可为用户带来很多好处,这里将讨论其中的一些,包括低复杂度、低链接延迟和实现确定性延迟的简单方案。

JESD204B是一种新型的基于高速SERDES的ADC/DAC数据传输接口。随着ADC/DAC采样速率的不断提高,数据的吞吐量也越来越大,对于500MSPS以上的ADC/DAC,动辄就是几十个G的数据吞吐率,而采用传统的CMOS和LVDS已经很难满足设计要求,这个时候,JESD204B应运而生。现在各大厂商的高速ADC/DAC上基本都采用了这种接口