一文搞懂DDR4 MIG IP核详细介绍与配置

judy 在 周二, 05/14/2024 - 10:38 提交

DDR4 SDRAM因其高速、大容量的特点,在FPGA设计中扮演着越来越重要的角色。本文将详细介绍DDR4 MIG IP核及其配置过程。

DDR4 SDRAM因其高速、大容量的特点,在FPGA设计中扮演着越来越重要的角色。本文将详细介绍DDR4 MIG IP核及其配置过程。

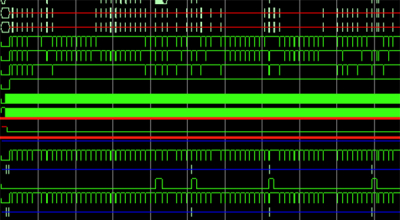

在生成example的时候,vivado就自带仿真激励的

查看MIG IP输出的init_calib_complete信号

话说之前从来没有使用过DDR,工作中的项目都是流式处理的

本文以XC7A35TFGG484-2这款芯片为例,采用米联客FPGA开发板,用MIG核驱动DDR3内存。FPGA外接的晶振大小为50MHz,DDR3内存的驱动频率(ddr3_ck_p和ddr3_ck_n)为400MHz。选用的DDR3内存型号为MT41K128M16,内存容量为256MB。

板子使用的是米联客的XC7A35TFGG484-2的开发板,上面带有256MB的型号为Micron MT41K128M16的DDR3内存。板子上的V4引脚上接了50MHz的晶振。

用MIG核来驱动这片DDR3内存。DDR3的运行时钟Clock Period为400MHz(由MIG核自己产生这个时钟,从ddr3_ck_p和ddr3_ck_n引脚输出出来,用来驱动DDR3)

本文以XC7A35TFGG484-2这款芯片为例,采用米联客FPGA开发板,用MIG核驱动DDR3内存。FPGA外接的晶振大小为50MHz,DDR3内存的驱动频率(ddr3_ck_p和ddr3_ck_n)为400MHz。选用的DDR3内存型号为MT41K128M16,内存容量为256MB。