PCIe如何紧随计算和网络步伐?

judy 在 周二, 04/30/2024 - 10:23 提交

当系统架构师坐下来设计他们的下一个平台时,他们首先会查看 CPU、加速器、内存、闪存、网络接口卡以及 PCI-Express 控制器和交换机供应商提供的一系列路线图

当系统架构师坐下来设计他们的下一个平台时,他们首先会查看 CPU、加速器、内存、闪存、网络接口卡以及 PCI-Express 控制器和交换机供应商提供的一系列路线图

本教程提供一个最小的参考设计,使上柆机可以通过PCIE端口

硬件在分配PCIE的管脚的时候,没有分配到xilinx推荐的对应的管脚上,如何处理呢?

本文总结了Vivado 2023.1 中针对不同 Versal PCIe IP 的 10 位标签请求器功能的支持信息

在 PCI Express 诞生 20 周年之际,我们回顾一下这一盛行的扩展插槽的过去和未来

当系统架构师坐下来设计他们的下一个平台时,他们首先会查看 CPU、加速器、内存、

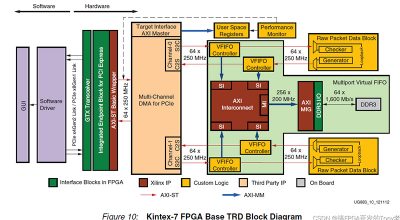

有客户需要通过PCie从Windows系统访问MPSoC的DDR,从而使X86和A53通过共享DDR内存的方式交互大量数据

Xilinx越来越多的例程,给出的参考设计是基于Block Design设计方法的

PCIe发展至今已经从最初的1.0升级到了6.0,但很多人对于PCIe只知其然而不知其所以然,小编今天就带大家一起来看一看

FPGA开发,虽然说行业应用千奇百怪,但是回归到平台设计这款,对外无非接口,对内无非片内总线