PCIE项目中AXI4 IP核例化详解

judy 在 周四, 10/27/2022 - 11:33 提交

本工程实现PCIE的8通道速率2.2GBps通信,并验证数据的正确性

本工程实现PCIE的8通道速率2.2GBps通信,并验证数据的正确性

本篇博文提供了一个示例,用于演示如何使用 Python 脚本调试赛灵思 PCIe 设计。此处提供的技巧可应用于所有设计,而非仅供 PCIe 专用。

实际使用中,Tandem PROM最为简单,Tandem PCIe由于允许通过PCIe进行重配置,因此在服务器领域最为常用。本文只介绍Tandem PROM方式。

如果要在 UltraScale+ 器件中执行手动眼扫描,重新排列程序会导致 PCIe 重新训练,降至第一代产品的速度,并停留在那里。

Versal™Premium 系列符合 PCIe® 规范修订版 5.0,并且通过每条通道每秒 32 千兆次传输的速度支持全部链路速率。该视频演示了 Versal Premium ACAP 中面向 PCIe 的两个可用子系统,这在下一代网络和云基础架构中至关重要。

在FPGA需要和处理器打交道时,无论是X86,还是PowerPC,以及一些嵌入式的ARM等,对外的接口常见如下表。

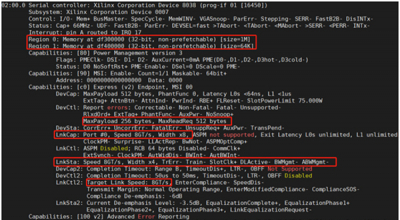

lspci 命令和 setpci 命令均为 Linux 发行版中原生可用的命令。这 2 条命令均可提供多级输出,适合在不同时间点用于查看 PCI 总线上训练的不同组件的功能和状态。其中大部分功能均可反映《PCI Express 基本规范》中所需的配置空间寄存器。

本章将着重讲述PCIe物理层组成与操作,物理层位于数据链路层之下,可产生PLP包(Physical Layer Packet)进行管理。

本章将着重讲述TLP的数据链路层组成与操作,上一篇更新应该为第五讲,数据链路层位于事务层和物理层之间,使用容错和重传机制保证了数据传输的完整性和一致性,此外,数据链路层还需要对PCIe链路层进行监控和管理。

本文将着重讲述TLP的存储器、配置、IO读写请求和原子操作、消息报文几种操作请求,其中主要从其结构和特点进行分析。