FPGA系列之“Zynq MPSoC PS-PL AXI Interfaces”

demi 在 周一, 02/10/2020 - 10:48 提交

本文主要介绍Zynq UltraScale+ MPSoC系列器件的PS-PL之间互连的AXI总线接口。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

本文主要介绍Zynq UltraScale+ MPSoC系列器件的PS-PL之间互连的AXI总线接口。

创建 FPGA 设计和维护 Vivado® 设计套件项目时,版本控制系统对于团队合作可能是一项具有挑战性的任务。工程师必须能跟踪设计变更,完整地从 HDL 或 TCL 源代码再现项目并交付特定的项目状态。

在不加时序约束时,Timing Report会提示很多的error,其中就有跨时钟域的error,我们可以直接在上面右键,然后设置两个时钟的伪路径。

很多FPGA初学者,都会怀疑学习FPGA有没有前途,发展前景怎么样,到底该怎样学习FPGA???各种迷茫,导致无法踏踏实实、全身心投入FPGA学习与开发工作中。下面请看看一个死磕FPGA 15年的大神给大家的肺腑之言,相信看完之后的你不在徘徊、不再犹豫、能够勇往直前。

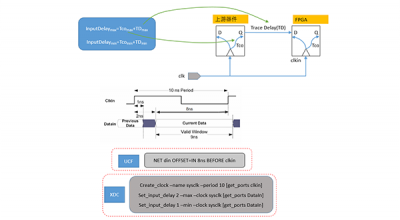

I/O约束是必须要用的约束,又包括管脚约束和延迟约束。管脚约束就是指管脚分配,我们要指定管脚的PACKAGE_PIN和IOSTANDARD两个属性的值,前者指定了管脚的位置,后者指定了管脚对应的电平标准。

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

跳频通信具有良好的抗干扰、抗多径衰落、抗截获等能力和同步迅速等特点,广泛应用于军事、交通、商业等各个领域。其关键技术主要有三点:跳频序列发生器、跳频频率合成器和跳频同步器。

① 滤波电容的放置要与电源接近,振荡器也是,在振荡器前端放电阻。② 通过Design的Board Shape改变电路板大小。

SPI——串行外围设备接口。是Motorola首先在其MC68HCXX系列处理器上定义的。SPI接口主要应用在EEPROM、FLASH、实时时钟,AD转换器以及数字信号处理器和数字信号解码器之间。SPI是一种高速,全双工,同步的通信总线,在芯片上只占用四根线(CS、MOSI、MISO、SCK),极大的节约了芯片的引脚。

git有多好用我就不用多说了,可谓是程序员必备技能之一。对于一般的软件代码来说,只需把源文件进行git管理即可。但对于FPGA工程师来说,使用git多多少少有几个问题......