FPGA时序约束理论篇之xdc约束优先级

demi 在 周一, 12/30/2019 - 14:45 提交

在xdc文件中,按约束的先后顺序依次被执行,因此,针对同一个时钟的不同约束,只有最后一条约束生效。虽然执行顺序是从前到后,但优先级却不同;就像四则运算一样,+-x÷都是按照从左到右的顺序执行,但x÷的优先级比+-要高。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

在xdc文件中,按约束的先后顺序依次被执行,因此,针对同一个时钟的不同约束,只有最后一条约束生效。虽然执行顺序是从前到后,但优先级却不同;就像四则运算一样,+-x÷都是按照从左到右的顺序执行,但x÷的优先级比+-要高。

“算力”在未来,就像当年的蒸汽机、电力一样,俨然已经是生产力发展的核心要素,也就是说,谁拥有超越别人的“算力”,谁就会拥有更高的生产力和效率,谁也就能在创新上实现真正的突破,成为推动产业和时代进步的原动力。所以“算力”会和“原力”一样成为人们期望拥有的能力。

在上一篇文章中,我们简要介绍了更高层次的问题,这些问题为优化加速器的需求奠定了基础。作为一个尖锐的问题提醒,现在让我们通过一个非常简单的图像分类算法,来看一看与之相关联的计算成本与功耗。

在 2014 年,斯坦福大学教授 Mark Horowitz 发表了一篇题目为“计算的能源问题(以及我们该怎么办)”的论文。 如果可以的话,我想借用并改编一下 Mark 的论文标题,这样我就可以就机器学习推断应用为什么应该考虑专用硬件,分享一下我的一些观点。

默认情况下,保持时间的检查是以建立时间的检查为前提,即总是在建立时间的前一个时钟周期确定保持时间检查。

因为ZYNQ 的PS 和PL 部分的电源有上电顺序的要求,在电路设计中,按照ZYQN 的电源要求设计,上电依次为1.0V -> 1.8V -> 1.5 V -> 3.3V -> VCCIO

AXI协议是基于burst的,主机只给出突发传输的第一个字节的地址,从机必须计算突发传输后续的地址。突发传输不能跨4KB边界(防止突发跨越两个从机的边界,也限制了从机所需支持的地址自增数)。

时钟周期约束,顾名思义,就是我们对时钟的周期进行约束,这个约束是我们用的最多的约束了,也是最重要的约束。

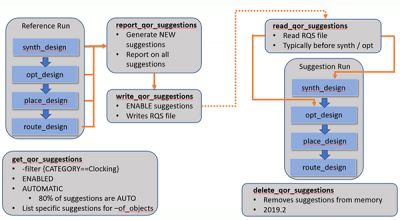

许多 FPGA 设计都难以达成所期望的性能目标。原因不尽相同,以下列出的只是其中部分可能的原因:未遵循 UltraFast 设计方法;时序约束不良;过高资源利用率;控制集过多;未采用最优化时钟设置;逻辑层次过多,难以达成目标性能;布局规划不良;布线拥塞;因约束导致工具优化受限。

前一篇文章《Python 中如何实现参数化测试?》中,我提到了在 Python 中实现参数化测试的几个库,并留下一个问题:它们是如何做到把一个方法变成多个方法,并且将每个方法与相应的参数绑定起来的呢?我们再提炼一下,原问题等于是:在一个类中,如何使用装饰器把一个类方法变成多个类方法(或者产生类似的效果)?