以 AMD 自适应计算技术进行虚拟制作

judy 在 周三, 02/19/2025 - 09:43 提交

推动虚拟影视制作转型的一项重要技术进步是采用现场可编程门阵列( FPGA )与自适应片上系统( SoC )器件。

推动虚拟影视制作转型的一项重要技术进步是采用现场可编程门阵列( FPGA )与自适应片上系统( SoC )器件。

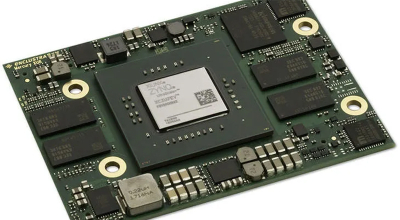

该系统可充分利用现有的HAPS-100生态系统,并支持混合的HAPS-200/100系统设置,可从单FPGA设置扩展到容量高达108亿门的多机架设置。

为提高网络弹性,系统设计人员可将FPGA集成到数据溯源系统中。与固定功能的处理器不同,FPGA作为真正灵活、可重新编程的硬件,能够进行并行处理和实时安全操作

你是否好奇,一段嘈杂的录音如何被分离出人声和背景音乐?一张模糊的照片如何通过算法变得清晰?

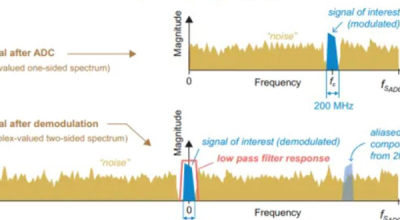

大多数SDR架构需要数字上转换和下转换阶段,这些转换位于A/D和数字基带级之间,包括信号的频率转换和采样率的变化。

最新的DisplayPort TX/RX 1.4 Subsystem IP v3.1支持eDP v1.4b, 支持下面的eDP features

测试和测量系统的主要任务之一是记录尽可能多的测量值。在这种情况下,基于FPGA的解决方案的优势就体现出来了,如固有的并行性、极高的带宽

SRIO是串行RapidIO的简写,其实现代比较常用的高速接口协议,比如SRIO、PCIE、JESD204B等都是基于SERDES开发的,均属于高速串行总线

在最新的DisplayPort 1.4 RX Subsystem IP GUI界面, 有使能Video EDID的选项, 如下: