【米联客-安路飞龙DR1-FPSOC】SDK入门篇连载-03 GPIO PS/PL实验

judy 在 周五, 08/23/2024 - 16:59 提交

本文对FPSoC芯片GPIO进行介绍,通过点亮PS LED和PL LED以及读取PL按键输入值,来控制LED灯闪烁,演示GPIO PS和GPIO PL的使用方法。

本文对FPSoC芯片GPIO进行介绍,通过点亮PS LED和PL LED以及读取PL按键输入值,来控制LED灯闪烁,演示GPIO PS和GPIO PL的使用方法。

AMD Xilinx的Versal器件中的PCIe IP,也可以作为PCIe Host。 AR76647 提供了相关驱动。

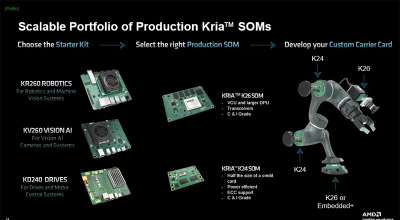

安富利在本次大会上,展出了基于AMD FPGA平台的适用于科学计算、工业视觉和边缘AI等应用领域的多款方案。

在当今数字化的时代,数字滤波器如同一位幕后的魔法大师,在众多领域施展着它的神奇魔力,悄然改变着我们的生活。那么,究竟什么是数字滤波器呢?

在这篇博客中,我们概述了这些标准的影响,以及系统设计人员过渡到PQC的基本步骤。

预计未来几年内,随着人工智能(AI)应用对处理能力需求的增加,AI加速器市场将持续快速增长。

本文介绍了I2S收发器的配置与实现,用于FPGA的VHDL编程。

7系列FPGA GTX和GTH收发器是功率高效的收发器,GTX收发器支持500 Mb/s至12.5 Gb/s的线路速率,GTH收发器支持13.1 Gb/s的线路速度

本方案是基于中科亿海微自主研发的EQ6HL45_CSG324型FPGA芯片,实现并满足了FOC算法的实时测量计算、电机参数的灵活配置、抵御噪声和电磁干扰等功能

边缘端的传感器和连接设备的数量每天都在以指数级速度持续增长。连接数字计算设备的模拟电子传感器使系统能够获得态势感知并优化性能