Vitis HLS OpenCV库编译

judy 在 周五, 02/18/2022 - 09:52 提交

Vitis HLS OpenCV库编译

Vitis HLS OpenCV库编译

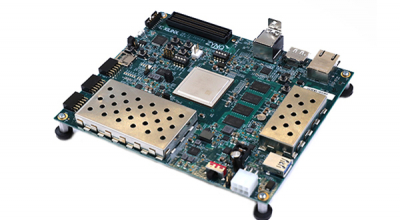

所有工具和参考设计使用2021.2。编译和测试X86主机(Host)的操作系统是CentOS 7.9.2009。测试的单板是VCK190,测试的是CPM QDMA。

提供给7系列FPGA收发器中PLL的参考时钟的质量可以极大地影响发送抖动和接收抖动容限的性能。参考时钟的抖动或相位噪声在决定这种性能方面起着重要作用--相位噪声是首选的规范方法

如图所示, 源文件目录中haha文件夹下有一个hoho.h头文件。本来要包含这个头文件应该写成#include "haha/hoho.h"的,但是如果写成#include

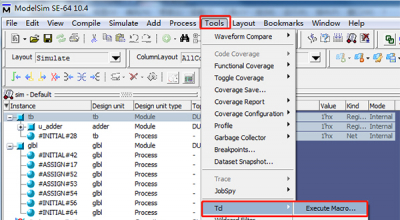

老鸟的姿势学起来,用脚本进行modelsim仿真

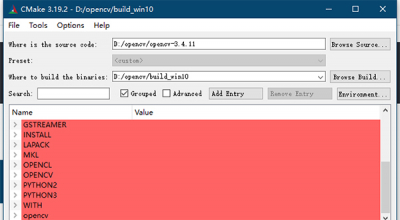

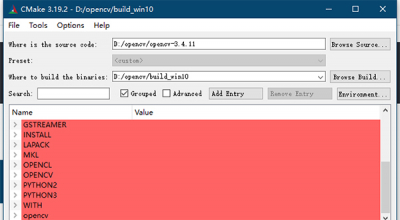

所有工具和参考设计使用2021.2。X86编译主机的操作系统是Ubuntu 18.04.6 LTS。

先从运行一个创建一个项目开始吧。

赛灵思 Versal® 套件计算加速平台 (ACAP) 设计方法论是帮助 Versal 设计流程的一整套计算实践。这必须让用户进行这些设计的操作下载能力和复杂性,因此通过特定的步骤设计任务确保设计完成并成功完成。

ZCU104 开发板基于Xilinx 公司Zynq UltraScale +XCZU7EV-2FFVC1156 MPSoC器件设计,支持嵌入式视觉使用案例的许多常见外设及接口

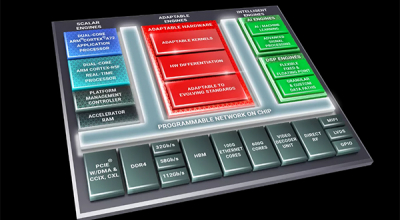

过去几年里,计算行业见证了数据的大规模爆发以及机器学习( ML )与 AI 应用的激增。其结果是对更高吞吐量和实时计算能力愈发强烈的需求,与此同时还要保持灵活应变能力,以便跟上不断演进的工作负载需求和不断变化的协议。