电子书申请:数据中心的 AI

judy 在 周二, 09/07/2021 - 17:30 提交

数据中心越来越多地采用人工智能来管理从设备监控到服务器优化的各种任务。基于 FPGA 的自适应计算处于数据中心的核心位置,在许多情况下,是运行复杂 AI 工作负载的最高效、最具成本效益的解决方案。阅读电子书,了解自适应计算如何助力加速。

数据中心越来越多地采用人工智能来管理从设备监控到服务器优化的各种任务。基于 FPGA 的自适应计算处于数据中心的核心位置,在许多情况下,是运行复杂 AI 工作负载的最高效、最具成本效益的解决方案。阅读电子书,了解自适应计算如何助力加速。

活动已结束,欢迎参加下届会议!

本篇笔记以点亮图中所有的LED为目的,回顾下Vivado的使用,并且开始了解Vitis的开发流程(原来开发环境为SDK)。

本文描述了推荐的设计方法,以实现对Xilinx® FPGA器件资源的有效利用,并在Vivado® Design Suite中更快地实现设计和时序收敛。提供了推荐方法背后的原因,以支持和实现明智的设计决策。

投票已结束!

SOC、SOPC、MPSOC、RFSOC、SDSOC的概念及区别

第四期课程是 PowerVR 性能建议指南的简化版本。它包含了开发人员在编写应用程序时应使用的各种经验法则和建议。在应用程序中实施这些技巧可能会对 PowerVR 设备上的应用性能产生重大影响。

在Vitis AI library中的模型在自定义单板使用中,介绍了如何进行模型库编译,下一步要将模型加入到AI应用中进行编译,生成可执行文件。

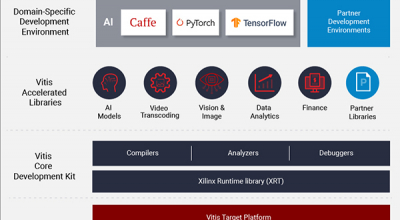

本系列笔记旨在更深入的探索Vitis以及Vitis内部所使用到的技术,本系列主要针对深度学习部署进行探索,比如自定义自己的深度学习硬件平台,深度学习模型量化、模型编译、TVM自动调优,多DPU核异构系统的调度计算等等。

本文通过使用 Design Gateway 的 TOE100G-IP 内核和 NVMeG4-IP 内核,在 Xilinx 的 KCU116 评估套件上演示了 TCP 卸载引擎网络和 NVMe SSD 实现的100Gbps 解决方案。