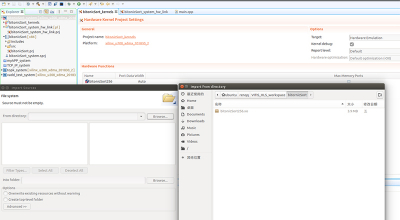

Vitis下Linux应用程序开发流程

judy 在 周五, 08/27/2021 - 09:55 提交

Vitis统一软件平台将Xilinx各种软件统一,即支持Vitis嵌入式软件开发流程,又支持Vitis应用软件加速开发流程。本文介绍Vitis嵌入式软件中的linux应用程序开发流程。

Vitis统一软件平台将Xilinx各种软件统一,即支持Vitis嵌入式软件开发流程,又支持Vitis应用软件加速开发流程。本文介绍Vitis嵌入式软件中的linux应用程序开发流程。

科通作为芯片产业的技术服务平台,与全球 50% 以上的高端芯片公司及众多国产芯片企业达成代理协议,连接上游百家以上的全球高端芯片供货商和下游数以万家的智能硬件公司,为他们提供芯片的应用设计方案和营销服务。近年来,凭借自身资源优势,科通基于自适应计算全球领导企业赛灵思公司的车规级高性能 Zynq®-7000 SoC 及 Zynq® UltraScale+ ™ MPSoC 系列芯片

本篇博文中的分析是根据真实客户问题撰写的,该客户发现不同操作系统间 QoR 性能存在差异。虽然可以理解赛灵思无法保证不同操作系统间的可重复性,正如"赛灵思答复记录 61599"中所述,但此处案例中出现的差异量级值得进一步深入调查。

HLS导出的.xo文件如何导入到Vitis里面?需要把.xo文件解压,然后把文件夹导入到Vitis Kernel/src文件夹下吗?

当前,各大车厂正在全力备战高级自动驾驶的量产,被称为自动驾驶智慧之“眼”的环境感知基础部件传感器,也进入了新一轮的技术迭代与创新升级的关键时期。业内一致认为,上一代的传感器配置已经不足以支撑L3级以上高级别自动驾驶的量产;单一传感器已经无法满足高阶自动驾驶应对复杂场景与安全冗余的需求,多传感器融合成为必然趋势。

本文描述 DPUCAHX8H,这是一种用于具有 HBM 的 Alveo 卡的高吞吐量 CNN 推理 IP。DPUCAHX8H 针对小图像尺寸网络进行了优化。

自动化可重复的工作、自主做出复杂决定,机器人正借由效率的提升持续改变着未来工作模式。机器人适应环境变化的能力越强,其所能提供的价值就越大。为什么固定功能芯片已难以满足机器人行业需求?

PYNQ结合了Zynq与Python的优势,是机器学习/人工智能、边缘计算、大数据处理等算法加速的优秀平台。PYNQ这个名字来自于Python productivity for Zynq,PYNQ使用Python语言简化了Zynq应用程序开发过程。

动态功能交换 (DFX) 在赛灵思芯片内赋能实现了巨大的灵活性,使用户能够按需加载应用,更新已经部署的系统并降低功耗。平台设计方便团队之间的协作,让一个团队专注于基础设施,另一个团队专注于硬件加速。然而,由于 DFX 有基础性的流要求,使得 Vivado 设计套件编译时间拖 长并给多用户环境造成挑战。

作为一支坚持前沿研究与客户需求双驱动的团队,赛灵思 AI 研发算法团队的研究领域覆盖应用算法优化,以及面向不同硬件平台的算法设计。本次 ICCV 录取的两篇论文就是这支团队在此领域收获的果实。