在Ubuntu18.04上安装Vivado Vitis Petalinux 2020.1

judy 在 周一, 08/23/2021 - 15:05 提交

Xilinx工具最新版本已经更新到2020.2,我之所以安装2020.1主要是因为PYNQ最新版本V2.6支持2020.1,今年会做一些PYNQ相关的开发。

Xilinx工具最新版本已经更新到2020.2,我之所以安装2020.1主要是因为PYNQ最新版本V2.6支持2020.1,今年会做一些PYNQ相关的开发。

基于FPGA的学习与创新要依赖硬件平台和器件,硬件借用是赛灵思开发者计划为其成员提供的一项重要权益。赛灵思SoC 开发板、系统级模块和 Alveo 数据中心加速器卡等核心平台已就位,旨在提供必要的资源帮助有独立开发能力的成员更快地构建应用程序,同时结合全新的赛灵思Vitis统一软件平台,加速开发者在加速计算、人工智能和机器学习等各个领域实现应用创新。

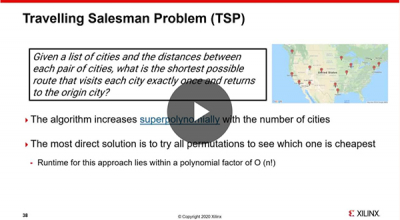

变革性的高性能应用设计似乎令人望而却步,但凭借自适应计算,您可优化硬件以实现更高的效率,并以超出预期的速度将创新成果推向市场。本视频将为您揭晓...

赛灵思 Versal™ 自适应计算加速平台 (ACAP) 设计方法论是旨在帮助精简 Versal 器件设计进程的一整套最佳实践。鉴于这些设计的规模与复杂性,因此必须通过执行特定步骤与设计任务才能确保设计每个阶段都能成功完成。遵循这些步骤和最佳实践进行操作,这将有助于以尽可能最快且最高效的方式实现期望的设计目标。

超越 CPU 及 GPU 性能的Vitis加速应用 C++ 内核开发实例

近日,高阶FPGA ( Field Programable Gate Array可编程逻辑门阵列)系统设计、培训、技术咨询及大学计划的定制化服务专家依元素科技与美国赛灵思(Xilinx,Inc.,以下简称Xilinx)携手赞助的第五届台湾地区「创创AIoT竞赛」,因应台湾地区防疫政策原因,修改采用以在线方式举行盛大的总决赛。

在文章中如何将zcu106例程移植到自定义单板,描述了如何在自定义单板平台构建硬件平台、软件系统添加配方,运行zcu106例程。实现过程很复杂。zcu106单板的bsp不能直接用在习惯单板上呢?下面是我做的一些试点,大家可以参考。

本篇博文中的分析是根据客户真实问题撰写的,该客户发现即使时序已得到满足的情况下,硬件功能仍出现错误。最后发现,问题与时钟域交汇 (Clock Domain Crossing) 有关,因此,本篇博文介绍了如何调试设计中的时钟域交汇问题。