ADC/FPGA串连顺畅 JESD204B界面故障排除无碍

judy 在 周四, 08/19/2021 - 11:31 提交

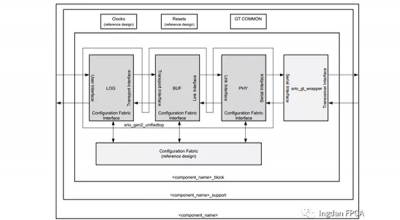

本文阐释了JESD204B标准的ADC与FPGA的接口,如何判断其是否正常工作,以及可能更重要的是,如何在有问题时排除故障。文中讨论的故障排除技术可以采用常用的测试与测量设备,包括示波器和逻辑分析仪,以及Xilinx的ChipScope或Altera的SignalTap等软件工具。同时说明了接口讯号传输,以便能够利用一种或多种方法实现讯号传输的可视化。

本文阐释了JESD204B标准的ADC与FPGA的接口,如何判断其是否正常工作,以及可能更重要的是,如何在有问题时排除故障。文中讨论的故障排除技术可以采用常用的测试与测量设备,包括示波器和逻辑分析仪,以及Xilinx的ChipScope或Altera的SignalTap等软件工具。同时说明了接口讯号传输,以便能够利用一种或多种方法实现讯号传输的可视化。

在zcu106开箱即用vcu示例中用到了USB摄像头,本节介绍如何对摄像头输出图像进行编解码。

为了使广大开发者学新学透,赛灵思开发者社区与电巢直播间特别邀请到两位赛灵思专家为大家分享Vitis及Vitis AI是如何在赛灵思异构平台(包括FPGA, SoC, Versal ACAP) 上实现嵌入式软件和加速应用。欢迎您点击关注,届时收看。

了解嵌入式软件(如 Linux、Xen Hypervisor 和免费实时操作系统)在 2021.1 发布周期中的新特性,以及构建工具(如 Yocto 和 PetaLinux)和 VCU 软件的最新信息。该视频将详细介绍在该发布周期中所有的新增功能与修改内容。

随着PCIe接口、以太网接口的飞速发展,以及SOC芯片的层出不穷,芯片间的数据交互带宽大大提升并且正在向片内交互转变;SRIO接口的应用市场在缩小,但是由于DSP和PowerPC中集成了SRIO接口,因此在使用DSP/Power PC + FPGA的使用场景中仍然占有一席之地。

赛灵思FPGA平台出色的性能和简洁易用的 Vivado™开发工具,助力小鸟科技将业界领先的专业音视频解决方案性能提升1.5倍,并提前半年推向市场。

过去 20 年里,金融交易领域风起云涌:电子交易、算法、智能订单路由器持续演进;高频交易( HFT )兴起;为追求增强收益而寻找更复杂搜索策略。伴随这些趋势,金融交易指令也经历了重大变化。无论使用或编写哪种算法,在降低时延、保持性能的同时提升算法精密度和准确度,总是不变的需求。毕竟,竞争永无休止。

Xilinx的开发工具SDK/Vitis都可以自动根据Vivado设计,创建软件工程,自动配置各个外部设备的驱动程序。为了兼容旧版本工程,SDK/Vitis里提供了多个IP版本的驱动程序。如果在SDK/Vitis的软件工程里查看代码,驱动程序都是正确的。

是德科技(Keysight Technologies Inc.)日前与赛灵思(Xilinx)和思科(Cisco)共同展示一套创新的前传解决方案,可协助行动通讯业者从传统4G LTE网路,平顺地转移到5G开放式无线接取网路(O-RAN)。

工业市场和医疗市场上的各类视觉应用,都期待摄影机的尺寸、速度、智能性和功耗水平能获得改善,特别是工业应用还对安全性、扩展温度效能和生命周期,有着更额外的要求。本文将探讨机器视觉、工厂自动化和机器人技术等应用中的部分此类需求。