将自适应计算运用至广泛的市场

judy 在 周五, 08/06/2021 - 09:31 提交

软件和 AI 营销副总裁 Ramine Roane 将讨论行业趋势,并带您了解最新的 Xilinx 解决方案和最新产品介绍。了解 Xilinx 自适应平台如何提高加速计算的标准。

软件和 AI 营销副总裁 Ramine Roane 将讨论行业趋势,并带您了解最新的 Xilinx 解决方案和最新产品介绍。了解 Xilinx 自适应平台如何提高加速计算的标准。

本次设计目标是将ZCU106使用的例程移植到自定义单板上。例程指的是pg252中开箱即用7个例子。

Xilinx 器件及 Vitis/Vitis AI 解决方案可为众多应用加速,包括视频处理、图像预处理、AI 推断以及内存带宽优化等。在本视频中,我们将演示如何使用 Xilinx ZCU104 开发人体检测应用。我们不仅将展示 Vitis AI 堆栈如何实现高速度、高精度和高性能,而且还将展示如何使用 Vitis HLS 库、DRM 以及 V4L2 等工具实现进一步优化。

如今,在赛灵思应用商店中,您将能轻松地获得一款来自 Aupera 的端到端人脸识别商业可部署解决方案,该解决方案基于赛灵思 Alveo® 加速器卡和 Zynq™ SoC,提供了业界领先的识别准确度和低时延,同时以较低硬件投资带来无与伦比的性能,并确保同类最佳的总体拥有成本。

本文在上篇基础上描述在FZU3上运行DPU例程的方法。

今天,先来推荐XILINX比较新的系列, Zynq Ultrascale+ MPSoC系列,主要针对中高端市场需求。Zynq® UltraScale+™ MPSoC 器件不仅提供 64 位处理器可扩展性,同时还将实时控制与软硬件引擎相结合,支持图形、视频、波形与数据包处理。置于包含通用实时处理器和可编程逻辑的平台上

为了提升计算基础设施的性能,并紧跟数据分析与 AI 不断攀升的需求,众多企业将硬件加速视为主要的解决方案。在大多数情况下,先进的可编程硬件(主要是指 GPU 和 FPGA)是加速的主要方式。通过使用这种先进的硬件,企业正在赢得计算优势;然而,对于编程难度,他们仍然存在合理的担忧。

在软件和硬件开发过程中,我们经常要使用到版本控制系统,也就是 Version Control。在这个视频中,简要介绍如何使用git在Vitis IDE中进行版本控制,并做一个简短的演示。

上周四,2021赛灵思技术日(XTD)首站在北京圆满落幕。赛灵思高层、技术专家以及学术、产业界嘉宾奉上精彩演讲,同时带来多款基于自适应平台的现场 demo 演示,为北京站主题“‘适’逢芯动,聚‘创’未来”增添了完美注解。

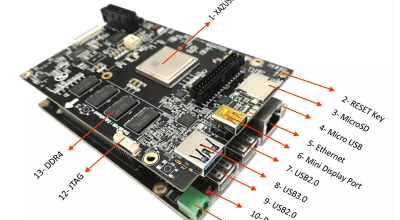

百度Edgeboard FZU3硬件平台构建和软件系统构建