Vitis AI 库概述

judy 在 周二, 07/27/2021 - 09:21 提交

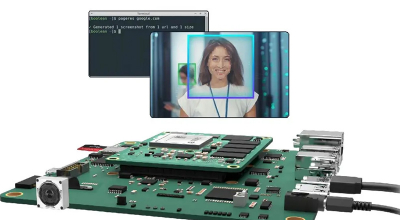

本视频描述了 Vitis AI 安装说明、如何设置环境、以及如何安装 Vitis AI 目标板的依赖项。

本视频描述了 Vitis AI 安装说明、如何设置环境、以及如何安装 Vitis AI 目标板的依赖项。

由 AI 提供支持的应用,正在日益普遍地被部署到边缘和终端,高性能 AI 推断正在推动更智慧的城市和高度自动化的智能工厂步入现实。随着智能零售引入了极为精致的自动化购物体验,零售体验也变得更加精巧细腻。这些应用需要具备极高可靠性并提供高性能,同时也需要提供高效紧凑的外形尺寸。

该设计咨询涵盖如下 UltraScale+ GTH/GTY 收发器问题,即 GTPOWERGOOD 在上电后可能无法断言有效。所有 UltraScale+ GTH/GTY 收发器中均包含 *_delay_powergood.v 模块。

毕设要用到Xilinx家的ZCU106这块板子,了解到最近Xilinx统一了Vivado,XilinxSDK,并集成了常用开源IP核,推出了Vitis统一软件平台,使我们不再需要关注底层的Verilog实现,因此尝试使用Vitis开发一个神经网络加速器,作为毕设的基础。

Versal Premium HSC 或高速加密块可为 Versal 系列带来高达 400G 的 AES-128/256 加密和解密功能。 在本演示中,我们将展示 HSC 模块的功能以及它与其它硬 IP 协作的原理并快速演示该模块本身在当前硬件中的工作情况。

新的挑战需要灵活应变的解决方案,既要能够处理多样化的需求,同时也要能够随市场需求的变化而持续演进发展。Zynq® UltraScale+™ RFSoC DFE因其架构上集成了比传统软逻辑更多的硬化 IP 逻辑, 使得其在保持赛灵思一贯的灵活应变价值的同时,还能媲美定制 ASIC 在成本和功耗上的竞争力,因此能轻松应对这些挑战。

SmartLynq+ 模块的构建旨在满足高速调试和跟踪需求,主要面向使用Versal™ 平台的开发者。与此前的赛灵思调试产品相比,SmartLynq+ 模块通过 HSDP 可将 Linux下载时间加快高达28倍,将数据捕获速度提高100倍。更快的迭代和重复下载既提高了开发效率,也缩短了设计周期。

ElectroKnox 需要为前沿汽车应用、服务和安全建立通用且强大的基础。该公司的 SGW1000 汽车智能网关解决方案是一种基于赛灵思 Zynq UltraScale+ MPSoC 平台的软硬件统一平台解决方案。该方案支持 OEM 厂商快速在软件中开发功能,并缩短上市进程,让“软件定义汽车”的理念进一步贴近现实。

大学生方程式汽车大赛(Formula Student)是全球最大的工程师竞赛。得益于创新的、基于FPGA模块的电动传动系统,位于瑞士苏黎世的AMZ学生团队成功问鼎这项赛事。AMZ团队的赛车配备了4台基于Enclustra(瑞苏盈科)水星Mercury ZX5核心板(基于XilinxZynq 7015 SoC)打造的逆变器,创造了最快圈速。

多地巡回、连续数月,究竟是怎样一款产品令安富利为其精心筹备了一连串活动? 如何跨越AI系统的开发门槛成为一名“高级玩家”?拥有一款“开箱即用”的开发套件是种怎样的体验?